编辑同道:

随着各国在芯片制造领域的竞争不断加剧,时常看到新闻中涌现“28纳米”“14纳米”“7纳米”等提法。叨教芯片制程所说的“几纳米”指的是什么?

山东读者 宋非

作为打算机、移动终真个核心元器件,小小一枚芯片上,每每集成着数亿、数十亿个晶体管,以实现运算功能。如果将芯片比作屋子,那么晶体管便是盖屋子的砖块。随着技能发展,对芯片的性能哀求不断提高,单个芯片上集成的晶体管数量也越来越多。而综合考虑便携性、发热量等问题,芯片的大小是有限的。如何尽可能多地增加晶体管数量,就成了技能攻关的重中之重。对此,行业给出的同等答案是:把晶体管的体积只管即便缩小。

资料图

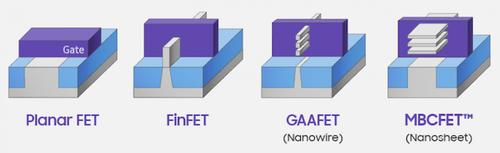

一样平常来说,芯片的纳米数,指的是芯片的制造工艺,或者晶体管电路的大小,单位是纳米。纳米是长度单位,即是十亿分之一米。在处理器芯片中,晶体管之间的间隔便是间距。例如,晶体管间距为10纳米的芯片,就可称为“10纳米工艺”。晶体管间距越小,意味着同样尺寸的芯片上可以集成的晶体管就越多,芯片的构培养越繁芜,相应地具有越强的性能和越低的功耗。

当然,巨大的益处也带来了极高的技能寻衅。实际上,芯片的制造工艺并不能无限缩小,特殊是10纳米以内。一颗原子的大小约为0.1纳米,即便是“较大”的10纳米工艺,也仅有不到100颗原子的宽度。只要有一处毛病,产品就会涌现故障,成为“废品”。因而想要实现大规模量产,需战胜关键技能、制造设备、良品率等诸多难关。

目前,处理器芯片的主流制造工艺都已迈进10纳米大关,且仍在高速发展。据宣布,作为芯片的载体,晶圆的制造厂商台积电正持续发力攻关2纳米及3纳米工艺,个中3纳米工艺的芯片估量将于2024年下半年投产。三星等其他厂商也有相应动作。

市场霸占率方面,互联网数据中央报告显示,截至2022年年底,台积电和三星分别为晶圆代工厂商的第一、第二位。(佟云翀)