随着半导体技能的不断发展,用户对 PCIe 高速接口的需求也在显著增加。

以当前热推的 PCIe 5.0 为例,其带宽在短短几年内,就翻番到了 PCIe 3.0 时期的四倍。估量不久后,我们还将看到 PCIe 6.0 的身影。

须要指出的是,只管芯片组支持的数据传输速率越来越高,行业在全体系统的开拓和设计上却碰着了越来越大的困难。

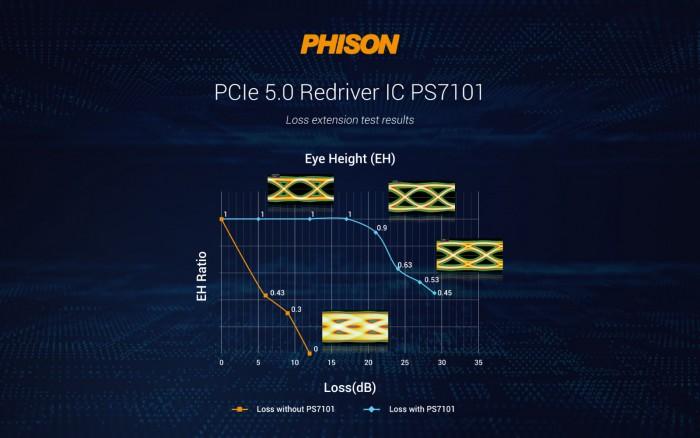

详细说来是,主板上的噪声、衰减和滋扰,终极会导致 CPU 芯片与端点之间的旗子暗记无法准确传输,乃至引发一系列兼容性问题。

好是,群联新发布的 PS7101 中继芯片,就能够有效降落 CPU 与终端连接时可能涌现的兼容性问题。

此外该公司的 Flip-Chip 设计,还可进一步降落 IC 封装带来的旗子暗记反射和串扰滋扰,同时提升芯片的散热能力。

据悉,PS7101 供应了多频段独立补偿,可轻松适应不同的布线或 PCB 材料,使得开拓互助伙伴能够更好地调度其电旗子暗记,以实现最佳的损耗补偿。

值得一提的是,群联还为客户供应了具有专利的 Auto Tuning 自动调校工具。

该工具可为客户的 Redriver 开拓环境自动设置不同的增益参数,采集旗子暗记结果,并通过 AI 技能供应优化,以找到适宜相应环境的最佳参数

随着主流 CPU / 主板芯片组制造商不断将 PCIe 的传输速率推向极限,行业生态系统也必须供应完善的技能支持。

在听取了客户需求之后,群联创记录地只用了 8 个月的韶光,即完成了 PS7101 的 IC 规格设计、出样、测试、以及投产。

经由严格的测试,群联致力于确保每项 IC 所需的特性,都可知足规范的哀求,同时确保不同 CPU 芯片和 PCIe 5.0 设备之间繁芜多样的传输环境的兼容性。

群联董事长兼首席实行官 K.S. Pua 表示:

我们是少数有能力开拓 PCIe 5.0 SerDes PHY IP 的 ASIC 企业之一。

我公司的高速接口工程团队积累了多年履历,涵盖从 USB、SATA、USF 接口的 IC 技能开拓,到成功推出自研 PCIe 4.0 SSD主控。

此外群联在提升兼容性、旗子暗记剖析和仿真系统上也投入了巨资,建立了前辈的高速旗子暗记剖析实验室,为向高端市场进军而奠定了坚实的根本。