一、传统封装

传统封装观点从最初的三极管直插期间开始产生。传统封装过程如下:将晶圆切割为晶粒(Die)后,使晶粒贴合到相应的基板架的小岛(LeadframePad)上,再利用导线将晶片的接合焊盘与基板的引脚相连,实现电气连接,末了用外壳加以保护。范例封装办法有DIP、SOP、QFP等。

只管表面贴装封装比通孔插装封装具有很多的上风,但由于表面贴装封装在PCB上的安装密度高,对散热的哀求更高;同时,由于器件与PCB的热膨胀系数(CTE)不同,随意马虎造成焊点处涌现裂纹乃至开裂。最严重的是塑封体的吸湿问题,由于表面贴装封装在焊接时塑封体整体受热,随意马虎造成塑封体接管的水汽受热膨胀而产生内部分层征象,严重时可能产生塑封体爆裂。

由此可见,表面贴装封装与通孔插装封装比较,差异不仅是形状的不同,也是对集成电路芯片设计、封装构造设计、封装材料、检测技能和相应的设备提出了更高的哀求。

当然,通孔插装类封装具有焊接方便、可靠性好、易于维修、对材料湿气敏感哀求低、散热性能好、功率大等特点,常日利用在对体积哀求不严苛的场合,也可用于大功率器件的封装。因此,到目前为止,通孔插装类封装仍霸占着一定的市场份额。

二、前辈封装

进入21世纪,随着半导体技能逐渐逼近硅工艺尺寸的极限,半导体技能进入“后摩尔定律”时期,前辈封装技能得到了空前发展。涌现于20世纪末的多芯片组件(MCM)封装、系统级封装(SiP)、三维立体(3D)封装和芯片尺寸封装等技能快速发展,并被广泛运用。同时,系统级芯片(SoC)封装、微机电系统(MEMS)封装、硅通孔(TSV)技能、凸点制作(Bumping)、表面活化室温连接(SAB)等技能实现了新的打破,并已实现批量生产。

(1)倒装芯片(FC)技能

FlipChip指的是芯片倒装,以往的封装技能都是将芯片的有源区面朝上,背对基板贴装键合。而FlipChip则将芯片有源区面对着基板,通过芯片上呈阵列排列的焊料凸点(Bumping)实现芯片与基板的互联。其工艺过程为:先在芯片上制作金属凸点,然后将芯片面朝下利用焊料直接与基板相连,常日会利用底部添补(Underfill)树脂对热应力进行再分布来提高可靠性。其优点是封装面积减小,引线互连长度缩短,引脚数量增加。

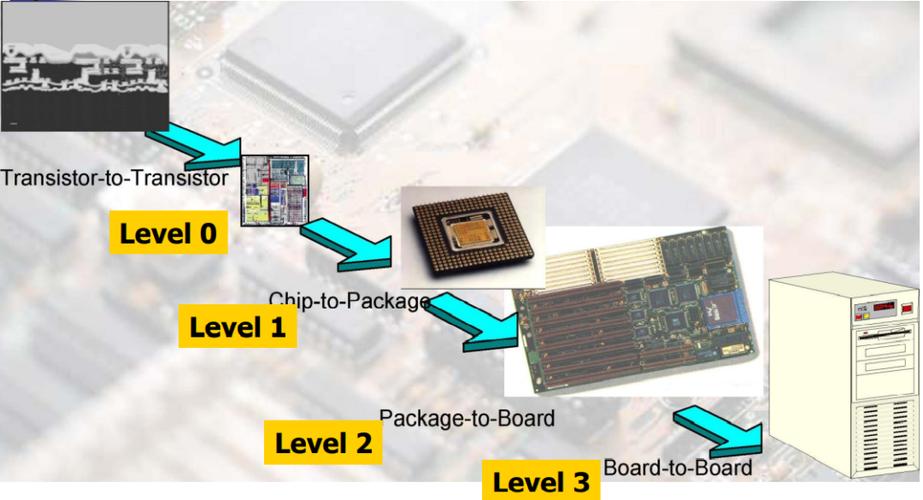

传统封装和前辈封装构造比拟

(2)晶圆级封装(WLP)技能

在传统封装观点中,晶圆是先被切割成小的晶粒,之后再进行连接和塑封。而晶圆级封装(Wafer-levelpackaging(WLP))工序恰好相反,是直接以圆片为加工工具,同时对圆片上的浩瀚芯片进行封装及测试,末了切割成单颗成品,可以直接贴装到基板或PCB上,个中紧张工艺为再布线(RDL)技能,包括溅射、光刻、电镀等工序。WLP封装时裸片还在晶圆上,一样平常来说,WLP是一种无基板封装。WLP利用由布线层(routing layers)或重新布线层(RDL)构成的薄膜来代替基板,该薄膜在封装中供应电气连接。RDL不会直接与电路板连接。相反,WLP会在封装体底部利用锡球,从而将RDL连接到电路板。具备两大上风:(1)将芯片 I/O 分布在 IC 芯片的全体表面,使得芯片尺寸达到微型化的极限。(2)直接在晶圆片上对浩瀚芯片封装、老化、测试,从而减少常规工艺流程,提高封装效率。

扇入型封装、倒装芯片与扇出型封装技能的比较

WLP又经历了从Fan-in WLP(WLCSP)向Fan-out WLP(FOWLP)的演进,Fan-in WLP是在 wafer 未进行切片前对 wafer 进行封装,之后再进行切片分割,完成后的封装大小和芯片尺寸同等,该构造的芯片面积尺寸和终极的封装体面积尺寸为标准的1:1,扇入式 WLP 是一种独特的封装形式,并具有真正裸片尺寸的显著特点。具有扇入设计的 WLP 常日用于低输入/输出(I/O)数量(一样平常小于 400)和较小裸片尺寸的工艺当中。

Fan-Out WLP技能初始用于将独立的裸片重新组装或重新配置到晶圆工艺中,并以此为根本,通过批量处理、构建和金属化构造,如传统的扇入式 WLP 后端处理,以形成终极封装。其工艺过程为先将芯片作切割分离,将芯片重新布局到一块人工晶圆上,然后将芯片正面朝下黏于载具(Carrier)上,并且芯片间距要符合电路设计的节距(Pitch)规格,接着进行封胶(Molding)后形成面板(Panel),后续将封胶面板与载具分离,可实现在芯片范围外延伸RD以容纳更多的I/O数。

随着金线价格的上涨,一些公司也正在考虑采取 WLP 作为低本钱替代方案,而不是采取引线键合封装,尤其是针对更高引脚数的器件。最近几年中,WLP 也已经被广泛用于图像传感器的运用中。目前,硅通孔(TSV)技能已被纳入用于封装图像传感器的 WLP 办理方案。其他更新的封装技能也在逐渐发展,并与现有的 WLP 技能进行整合,例如三维(3D)集成技能。

(3)平板级封装(PLP)技能

PLP:全称Panel-levelpackaging,平板级封装,封装方法与FOWLP类似,只不过将晶粒重组于更大的矩形面板上,而不是圆形的晶圆。更大的面积意味着节约更多的本钱,更高的封装效率。而且切割的晶粒为方形,晶圆封装会导致边角面积的摧残浪费蹂躏,矩形面板正好办理了摧残浪费蹂躏问题。但也对光刻及对准提出了更高的哀求。

(4)微系统封装技能

微系统封装技能(Micro System Packaging)是指将多个功能芯片,用必要的配件和装置平台,按照系统最优的原则进行集成、组合,从而构成运用产品的封装技能。微系统因此微电子技能、射频技能、无线电技能、光学(或光电子学)技能、微机电系统(MEMS)等技能为核心,从系统工程的高度出发,通过包封、互连等微细加工技能,在框架、基板等载体上制造、装置、集成出眇小化的功能装置。微系统封装技能,根据其微系统定义的不同,分为微电子封装技能、射频封装技能、光电子封装技能、微机电系统封装技能和多功能系统集成封装技能等多个方面的封装技能。

在全体MEMS生态系统中,MEMS封装发展迅速,晶圆级和3D集成越来越主要。紧张的趋势是为低温晶圆键合等单芯片集成开拓出与CMOS兼容的MEMS制造工艺。另一个新趋势是裸片叠层运用于低本钱无铅半导体封装,这种技能可为量产带来更低的本钱和更小的引脚封装。但是,MEMS器件的CMOS和3D集成给建模、测试和可靠性带来寻衅。

三、集成电路封装类型的选择

封装类型的选择是IC设计和封装测试的一个主要环节。如果封装类型选择不当可能会造成产品功能无法实现,或者本钱过高,乃至导致全体设计失落败。选择封装类型时,紧张从封装体的装置办法、封装体尺寸、封装体总引脚数、产品可靠性、产品散热性能、本钱等紧张方面综合考虑。

(1)封装体装置办法:选择封装类型的紧张事情便是确定装置办法,这直接决定电子产品封装完后的PCB设计及如何与PCB连接。封装的装置办法紧张有通孔插装和表面贴装两种。通孔插装便是将其表面的引脚利用插件的办法与PCB连接,如SIP和DIP封装类型;表面贴装是通过表面贴装技能将其快速地焊接到PCB上,如QFP,QFN,BGA,SOP等封装类型。

(2)封装体的尺寸:封装形式由于封装工艺的极限会对芯片尺寸(长度、宽度和厚度)有限定。在选择封装体时,首先担保芯片能够安装进封装体,再根据产品厚度哀求选择封装体厚度。随着消费类电子越来越朝轻、薄、短、小的方向发展,封装产品的厚度也越来越薄,选择封装体尺寸应优先选择小尺寸、薄型的封装体,以节约PCB的面积。

(3)封装体引脚数:所选择的封装体总引脚数应即是或大于集成电路芯片所须要的引出端总数(包括输入、输出、掌握端、电源端、地线端等)。

(4)产品可靠性哀求:塑料封装属于非气密性封装,抗湿润性能和机器性能相对较差,同时热稳定性也不太好,但在性能价格比上有上风;金属封装和陶瓷封装属于气密性封装,气密性、抗湿润性能好,散热性和机器性能好,但装置尺寸精度较差,价格较昂贵。因此,对付高可靠性的集成电路不宜选用塑料封装,而应选用陶瓷封装或金属-陶瓷封装,如军用和航天用产品;而一样平常工业用电子产品和消费用电子产品,由于其对可靠性哀求不太高且考虑本钱成分,一样平常会选用塑料封装。

(5)产品散热性能、电性能哀求:集成电路在事情时会产生大量的热量。在理解客户的散热性能需求和电性能哀求后,须要对选定的封装体进行热仿真和电仿真,以便确认是否知足散热性能哀求和电性能哀求。基于散热性能的哀求,封装体越薄越好。

(6)本钱哀求:对电子产品来说,封装本钱高会导致电子产品失落去市场竞争力,从而可能失落去客户和市场。一样平常来讲,对付同一种封装形式,大封装尺寸的产品比小封装尺寸的产品封装本钱高。对付不同的封装形式,基板产品比引线框架产品的封装本钱高;多层基板产品比单层基板产品封装本钱高;可靠性等级哀求高的产品比可靠性等级哀求低的产品封装本钱高。