也有人认为,制造7nm的芯片,可以用DUV光刻机,毕竟积电当年曾经用浸润式光刻机,多重曝光后,生产过7nm芯片。

台积电第一代7nm便是DUV光刻机制造的,第二代才换成EUV,以是第二代7nm工艺,台积电还称之为7nm EUV。

为什么大家要谈论这个呢?缘故原由在于我们目前买不到EUV光刻机,由于美国不准ASML卖给中国,而环球仅有ASML能制造EUV光刻机。

以是大家以为没有EUV光刻机,我们的芯片工艺,可能会止步于7nm。

那么问题来了,既然用DUV光刻机,能制造7nm芯片,那能不能再进一步,制造5nm芯片?

事实上也能,比利时微电子研究中央(IMEC),在去年的的时候,就发布了浸润式光刻机借助八重曝光做5nm的技能方案。

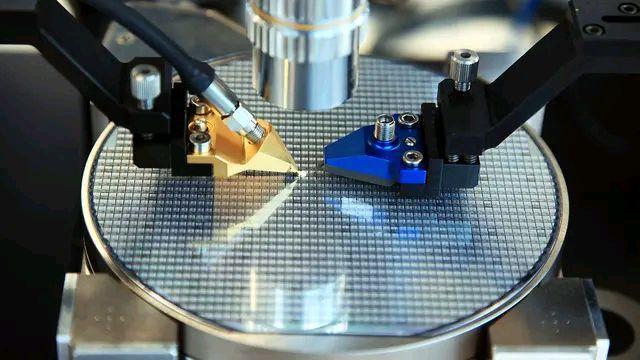

那如何来制造,和利用DUV光刻机,制造7nm芯片一样,采取多重曝光技能即可。目前多重曝光技能,还有很多种,常见的有LELE、LFLE、SADP。

所谓多重曝光,大略的来讲,便是以有一次光刻机,就将电路图刻上去了。而多重曝光,则是采取多次光刻,将电路图分解,末了组合。

而多重曝光最主要的便是套刻精度(Overlay),它决定了芯片高下层的对准精度,进而决定了多重曝光的良率。

举个有一点类似例子,一个“正”字,一次光刻的时候,表示一次性将“正”写刻出来,但要将“正”刻到足够小,一次性弗成,那就分成多次来刻,先横,再竖,再横……但这中间很主要的是,这么多次来刻的时候,组合后还是一个字,不能有偏移。

理论上来讲,只要套刻精度够,利用DUV光刻机,还能进一步的往5nm以下发展,3nm,2nm在理论上都是有可能的。

但是通过多次曝光后,芯片制造效率非常低,你想一想,原来一次就能光刻出来的芯片,要光刻多次了,速率不是慢了好几倍?本钱不是就高了?

其余套刻精度是一件非常麻烦的事情,由于没有谁能担保偏差即是0,而偏差大会导致坏的晶圆非常多,于是良率会降落,据称台积电用DUV制造7nm芯片时,良率也只有80%,如果台积电用DUV制造5nm,估计良率不会高于50%……

以是,在有EUV光刻机的条件之下,没谁还用DUV来制造5nm芯片,那就傻子才干的事情。

就算是我们,没有EUV光刻机,估计也不会真的用DUV来制造5nm芯片,由于没有什么必要,本钱高到无法商用,市场不会买单。

以是,大家就不要每天想着用用DUV光刻机,来制造5nm芯片了,就算制造的出来,也无法市场化,这是不现实的,还是想想其余的招吧,你以为呢?