而人类的大脑却并非如此,而是直接在影象体里打算。被认为具有“存算一体”潜力的忆阻器,因而成为类脑打算领域的热门器件。

近日,清华大学微电子所、未来芯片技能高精尖创新中央钱鹤、吴华强团队与互助者在顶尖学术期刊、英国《自然》杂志(Nature)在线揭橥论文,宣布了基于忆阻器阵列芯片卷积网络的完全硬件实现。

该存算一体系统在处理卷积神经网络(CNN)时能效比前沿的图形处理器芯片(GPU)高两个数量级,可以说在一定程度上打破了“冯诺依曼瓶颈”的限定:大幅提升算力的同时,实现了更小的功耗和更低的硬件本钱。

基于忆阻器芯片的存算一体系统 来源:清华大学

什么是忆阻器?

忆阻器,全称影象电阻器(Memristor),是继电阻、电容、电感之后的第四种电路基本元件,表示磁通与电荷之间的关系,最早由加州大学伯克利分校教授蔡少棠在1971年预言存在,惠普公司在2008年研制成功。

大略来说,这种组件的的电阻会随着通过的电流量而改变,而且就算电流停滞了,它的电阻仍旧会勾留在之前的值,直到接管到反向的电流它才会被推回去,即是说能“记住”之前的电流量。

这种奇妙的效果,实在和神经元突触有相仿之处。再加上忆阻器还具有尺寸小、操作功耗低、可大规模集成(三维集成)等优点,难怪打算机科学家们在忆阻器身上看到了存算一体、低能耗类脑打算的前景。

人工神经网络近年来大放异彩,如果用忆阻器连接成阵列,作为人工神经网络的硬件,会有什么效果?

忆阻器阵列

只管国内外许多企业、研究机构给予关注,但据清华大学新闻页面宣布,当前国际上的忆阻器研究还勾留在大略网络构造的验证,或者基于少量器件数据进行的仿真。基于忆阻器阵列的完全硬件实现仍旧有很多寻衅。

比如,器件方面,须要制备高同等、可靠的阵列;系统方面,忆阻器因事情事理而存在固有缺陷(如器件间颠簸,器件电导卡滞,电导状态漂移等),会导致打算准确率降落;架构方面,忆阻器阵列实现卷积功能须要以串行滑动的办法连续采样、打算多个输入块,无法匹配全连接构造的打算效率。

通过近年来积累的一些成果,钱鹤、吴华强团队逐渐优化材料和器件构造,制备出了高性能的忆阻器阵列。

2017年5月,该课题组就曾在《自然通讯》报告称,首次实现了基于1024个氧化物忆阻器阵列的类脑打算,将氧化物忆阻器的集成规模提高了一个数量级。这使芯片更加高效地完成人脸识别打算任务,将能耗降落到原来的千分之一以下。

忆阻器神经网络

这次,钱、吴团队集成了8个包括2048个忆阻器的阵列,以提高并行打算的效率。

在此根本上,他们构建了一个五层的卷积神经网络进行图像识别,得到了96%以上的高精度,结果显示,基于忆阻器的卷积神经网络比目前最前辈的GPU的能效要赶过两个数量级。

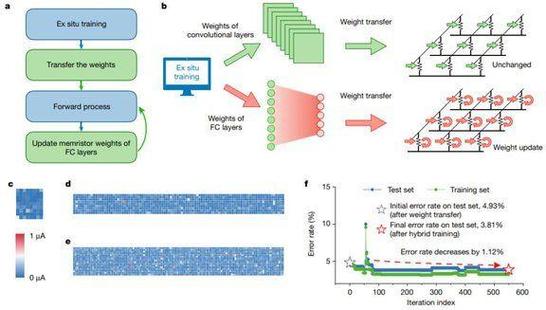

这样的提升是如何实现的?原来,为办理器件固有缺陷造成的系统识别准确率低落问题,他们提出了一种新型的稠浊演习算法,仅需用较少的图像样本演习神经网络,并微调了末了一层网络的部分权重。

与此同时,他们提出了空间并行的机制,将相同卷积核编程到多组忆阻器阵列中,各组忆阻器阵列可并行处理不同的卷积输入块,提高并行度来加速卷积打算。

多个忆阻器阵列并行处理

随着摩尔定律放缓,打算界翘首以待新的架构打破冯诺依曼瓶颈,适应越来越繁芜的AI问题。基于忆阻器的存算一体系统在这场竞赛中稳步提高。