知乎用户

中心处理器 (CPU)话题下的精良答主

74 人赞许了该回答

前阵子项目启动的时候,我卖力做全体流片流程的预算(是的便是我,我们组人手太少,做技能的还要出来客串一把财务唉说多了都是泪T_T),期间联系了全体流片流程中须要的各个步骤对应的一些公司,从制造到封装测试完全问了一圈下来,最贵的用度是正版合法的ip核授权,其次才是mpw tapeout,再其次是封装测试。

陆芯芯片切割机

TSMC mpw 40nm,联系到的报价单位都是按照block算的,最小计费单位是3mm x 3mm的一个block,我搜了一下我们得到的报价网上是没有的,以是不敢说单价了,我们的制造花费和封装测试花费大致上是7:3。前面有人说到fab对各个客户的报价不同,这个我们也创造了,业界有名的fab S家直接说跟我们没有互助关系谢绝报价,建议我们讯问和我们有关系的兄弟单位A来询价,结果兄弟单位A问到的S家报价比T家报价还高,而且明说要加收做事费 T_T 通过另一家跟T家关系更近的兄弟单位B问到的报价便是T家反而更低,囧。

如果要做一个正经的CPU,core自己写或者利用免费的开源版本,带个像样的MBytes级别的cache,能够起linux,DDR3和PCIE Gen3靠买合法ip的,后端仅仅哀求托钵人版配置,在TSMC 40nm这个节点上流片和测试封装,须要有一个千万级+的项目在背后支撑,不然很随意马虎捉襟见肘。至于其他人提及到的人工费,学术圈嘛,最不缺的便是劳动力 XD

期间联系过ARM的cortex-A系列IP,获知的情形和

@winnie Shao

先容的符合,同一个版本的前真个RTL代码被很多个公司和机构拿去在各种工艺下都流片过。

以上是做CPU的,做其他种类芯片的很可能完备不一致。

薛矽

芯片(集成电路)话题下的精良答主

227 人赞许了该回答

不同的流片渠道、流片规模、流片者的身份,纵然是在同一家Foundry厂的同一种制程下,流片价格都可能有很大的不同吧。

t家的保密事情很严,察看犹豫过涉密事宜,深究起来真的是六亲不认翻脸不认人,怕怕的,还是不要提和他家直接干系的统统事好了。

关于t家有一个冷知识(完备八卦,请勿相信):您知道为什么他家的logo上的字母是小写的么?由于小写的t和大写的T不同,大写的T是不出头的,小写的t某家才会有出头天。听说是某黄姓风水师的指示。听说某a家的电脑商也是如此这般(乱讲)。

用CIC(國研院晶片中央)最新(2015-3-9)的公开价目表供大家参考:

有tsmc,UMC(联电)的,业界和学界的价格也有一些差异。

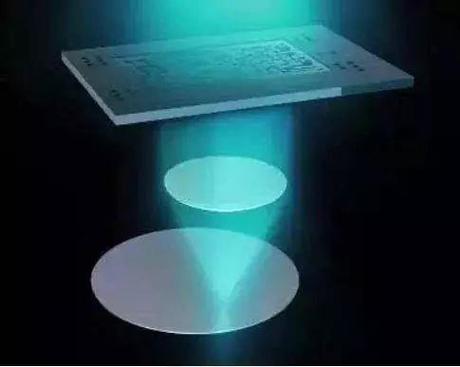

该当是可以做(或者便是)多项目晶圆(Multi Project Wafer,简称MPW)

比如透过CIC的这个管道(该当是只针对台湾的业界、学界,可能是已有优惠了的,CIC设立的初衷便是为台湾的IC家当供应良好的做事和保障),T家28nm,小面积下是大约23.5万软妹币每平方毫米;45nm大约是12万公民币每平方毫米(CIC公开报价)。拿起尺子看一看1毫米是种什么样的存在,会很震荡的。

(详细的报价单有官方的公开资料可以查询,这里就不放了。)

当然,这只是CIC的一种渠道,学界研究或传授教化还有很多别的渠道或优惠。

比如个人以为最逆天的是有T家.18 的“教诲线”,便是比如平时大学本科的模电课,一学期上完了,全班都可以申请流片做个放大器什么的,毕业设计更不用说了。这个渠道的T家.18是免费的。(真实的详细情形可能有出入)

台湾的IC设计强是有道理的。

身份所限还有很多有的没的就不多说了,本人真的什么都不知道,以上内容全来自公开网络。

T家的FinFET(16nm开始有用)干系的八卦我以为可以约请海思的工程师来答(当然基本上该当是什么也不能说,大学室友之前有在海思做版图,某天联结说要来T家出差一天,是为了某前辈工艺,彷佛是为了保密干系的缘故原由才须要人肉出差过来,不能在大陆做。)

其余,从设计者的角度,如果想更深入理解他家的新制程,可以在IEEE上搜Jack Yuan-Chen Sun、Bing J. Sheu两位Fellow的paper ,都是T家的Design方面研發大佬。老板约请他们来讲座的时候有先容说每一代前辈制程他们自己都有做深入的circuit design的研究(不但standard cell,包括一些Logic and Mixed-signal/RF technology),然后公布各种数据和剖析,比如2013 VLSI的这篇他们和胡正明教授一起揭橥的Invited paper:Enabling circuit design using FinFETs through close ecosystem collaboration. IEEE Xplore Abstract

How to design with finFETs

大陆也有好多类似的流片渠道和机构,比如上海ICC:

上海集成电路技能与家当促进中央

呆涛

芯片(集成电路)话题下的精良答主

76 人赞许了该回答

Cost=Masks+N×Wafers

价格 = 掩膜+N×硅片. 对付Full-Custom IC 来说, 掩膜占了紧张的价格.

题主只做数字逻辑的话, 有公司(Tekmos) 可以流"FPGA片", 便是底层金属是FPGA可控的连线, 然后上层金属是Fab制作. 大略地说, 便是为了一个Design来流FPGA的电影, 后期可控性比较好. 但是基本是0.35um 或者 0.6um的设计. 价格基本是按片论的. 好处是快(Tekmos担保两周出片), 可控性好, 比FPGA要优胜不少.

FPGA Conversions

正常的ASIC只许可设计到Gate Level, 也便是说你可以画Standard Cell, 但是不能再往下了. 大多数厂商都用的是这个设计.

本钱基本是0.5 Million起, 根据technology有不同.

Full-Custom便是可以自己随便设计所有的东西, 只要知足Design Rule. 以是本钱会比正常ASIC再高上一档. 一样平常流模电/高性能片 都得靠这个.

technology对价格影响多主要呢? 这么说吧:

对付 0.35u的技能, CMP一贯可以做到650 Euros/mm2, 换算起来的话约 4270 RMB. 每次40片 (CMP, 2013数据).

对付40nm来说, Full Custom IC的初流片本钱在2-3 Million(美金)级别 (CMP). 详细要看技能细节.

28nm更贵. 详细不理解(MOSIS天杀的不po他们家的价格...)

半导体工程师

半导体履历分享,半导体成果互换,半导体信息发布。半导体行业动态,半导体从业者职业方案,芯片工程师发展进程。