根据以上电路来说,由一个电源驱动多个负载,如果没有加任何电容,每个负载的电流颠簸会直接影响某段导线上的电压。

瞬间冲击电流的产生缘故原由

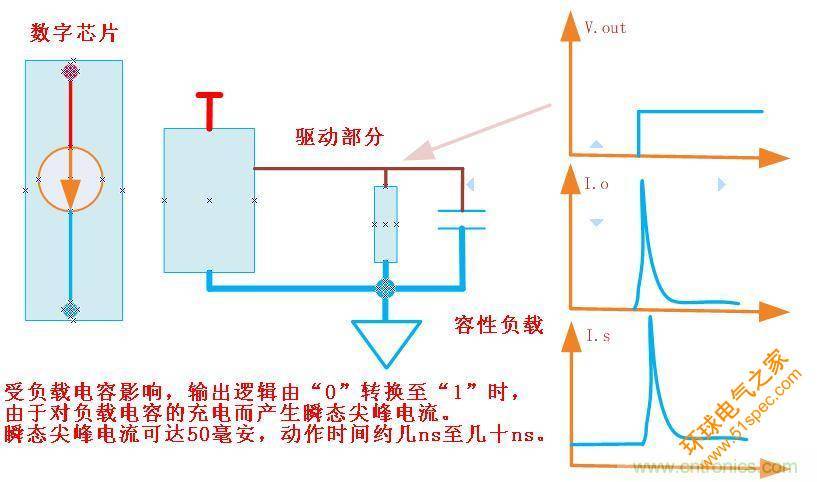

1.容性负载

来剖析一下数字电路的电流颠簸,数字电路的负载并不是纯阻性的,如果负载电容比较大,数字电路驱动部分要把负载电容充电、放电,才能完成旗子暗记的跳变,在旗子暗记上升沿比较陡峭的时候,电流比较大,对付数字芯片来说,新派驱动部分电流会从电源线上接管很大的电流,由于线路存在着的电感,电阻(特殊是芯片管脚上的电感,会产生反弹),这种电流相对付正常情形来说实际上便是一种噪声,会影响前级的正常事情,下图反应了事情情形

2.输出级掌握正负逻辑输出的管子短韶光同时导通,产生瞬态尖峰电流

PMOS和NMOS同时导通的时候涌现的电流尖峰。

电压塌陷噪声

我们考虑数字电路内部构造一样平常由两个Mos管组成,为了便于剖析,我们假设初始时候传输线上各点的电压和电流均为零。现在我们剖析数字器件某时候输出从低电平转变为高电平,这时候器件就须要从电源管脚接管电流(上面一个剖析的是容性负载,现在考虑的是阻性负载)。

从低到高(L=>H)

在韶光点T1,高边的PMOS管导通,电流从PCB板上流入芯片的VCC管脚,流经封装电感L.vcc,通过PMOS管和负载电阻末了通过返回路径。电流在传输线网络上持续一个完全的返回韶光,在韶光点T2结束。之后全体传输线处于电荷充满状态,不须要额外流入电流来坚持。

当电流瞬间涌过L.vcc时,将在芯片内部电源和PCB板上产生一个电压被拉低的扰动。该扰动在电源中被称之为同步开关噪声(SSN)或Delta I噪声。

从高到低(L=>H)

在韶光点T3,我们首先关闭PMOS管(不会导致脉冲噪声,PMOS管一贯处于导通状态且没有电流流过的)。同时我们打开NMOS管,这时传输线、地平面、L.gnd以及NMOS管形成一回路,有瞬间电流流过开关NMOS管,这样芯片内部至PCB地节点前处产生参考电平被抬高的扰动。该扰动在电源系统中被

称之为地弹噪声(Ground Bounce)。

实际电源系统中存在芯片引脚、PCB走线、电源层、底层等任何互连线都存在一定电感值,就全体电源分布系统来说来说,这便是所谓的电源电压塌陷噪声。

去藕电容和旁路电容

去藕电容便是起到一个小电池的浸染,知足电路中电流的变革,避免相互间的耦合滋扰。关于这个的理解可以参考电源掉电,Bulk电容的打算,这是与之类似的。

旁路电容实际也是去藕合的,只是旁路电容一样平常是指高频噪声旁路,也便是给高频的开关噪声提高一条低阻抗泄防路子。

以是一样平常的旁路电容要比去藕电容小很多,根据不同的负载设计情形,去藕电容可能差异很大,当旁路电容一样平常变革不大。关于有一种说法“旁路是把输入旗子暗记中的滋扰作为滤除工具,而去耦是把输出旗子暗记的滋扰作为滤除工具,防止滋扰旗子暗记返回电源”,我个人不太赞许,由于高频旗子暗记滋扰可以从输入耦合也可以从输出耦合,去藕的掉电可以是负载激增的输出旗子暗记也可以是输入旗子暗记源的突变,因此我个人以为怎么区分有点纠结。

电容模型剖析

如果电容是空想的电容,选用越大的电容当然越好了,由于越大电容越大,瞬时供应电量的能力越强,由此引起的电源轨道塌陷的值越低,电压值越稳定。但是,实

际的电容并不是空想器件,由于材料、封装等方面的影响,具备有电感、电阻等附加特性;尤其是在高频环境中更表现的更像电感的电气特性。

我们这里利用的电容一样平常是指多层陶瓷电容器(MLCC),其最大的特点还是由于利用多层介质叠加的构造,高频时电感非常低,具有非常低的等效串联电阻,因此可以利用在高频和甚高频电路滤波无对手。

关于其特性剖析和分类可以参考以前的文章:

Surface Mounted Capacitor(表贴电容) Ps:大部分是英文的,我有空把它翻译整理过来。

电容模型为

等效串联电阻ESR:由电容器的引脚电阻与电容器两个极板的等效电阻相串联构成的。当有大的互换电流利过电容器,ESR使电容器花费能量(从而产生损耗),由此电容中常用用损耗因子表示该参数。

等效串联电感ESL:由电容器的引脚电感与电容器两个极板的等效电感串联构成的。

等效并联电阻EPR:电容器泄露电阻,在互换耦合运用、存储运用(例如仿照积分器和采样保持器)以及当电容器用于高阻抗电路时,Rp是一项主要参数,空想

电容器中的电荷该当只随外部电流变革。然而实际电容器中的EPR使电荷以RC韶光常数决定的速率缓慢泄放。

通过上述参数,我们可以知道得到电容阻抗曲线

我找了Murata的电容做了比拟

1000pF 0402

100nF 0603

实际电容的阻抗是如图所示的网络的阻抗特性,在频率较低的时候,呈现电容特性,即阻抗随频率的增加而降落,在某一点发生谐振,在这点电容的阻抗即是等效串联

电阻ESR。在谐振点以上,由于ESL的浸染,电容阻抗随着频率的升高而增加,这是电容呈现电感的阻抗特性。在谐振点以上,由于电容的阻抗增加,因此对高

频噪声的旁路浸染减弱,乃至消逝。电容的谐振频率由ESL和C共同决定,电容值或电感值越大,则谐振频率越低,也便是电容的高频滤波效果越差。

ESL首先和电容的封装直接干系的,封装越大,ESL也越大。因此我们并联三个电容以上对付滤除噪声来说并不是很明显的。这里有个问题,我们乃至希望可以得到0402的0.1uF的电容,但是这个是比较难得,由于封装越小,操作电压和容值都是有限定的,以是理智的做法便是用两个电容。

通过曲线我们创造,如果我们只是考虑1MHz以内的噪声的时候,在大多数情形下,旁路电容的规则可以简化为只用0.1 μF电容旁路每一个芯片。不过我们要选择0603的MLCC的电容,而且要把稳电路布局。如果我们沿着电路板上的电流路线,可以创造电路板铜线上存在电感。在任何电流路径上的电感与该路径的闭环面积呈正比。因此,当你环绕一个区域对元器件进行布局时,你须要把元器件紧凑地布局(为了使电感为最低)。