2nm芯片研发成功,能耗降落性能翻倍,量产有多远?

今年十仲春末,台积电公布其2 nm制程的启动,预示著2 nm制程制程的问世有望在数年后实现。

2 nm制程的晶片虽已研制出来,但仍未量产。

由此产生的疑问是:2 nm的晶片到底有多强大?批量制造将面临什么样的难题?

2021年5月, IBM公司流传宣传他们的实验室已经研制出了环球首个2 nm的芯片。

就其效能而言,2 nm制程与现有7 nm制程比较,制程效率提升45%,制程功耗更可节省75%,且可达到三亿三千万/平方毫米的电晶体密度。

也便是说,最多500亿个电晶体可以被安置在一个指甲那么大的晶片中。这个密度比台积电的5 nm制程要赶过一倍。

2 nm芯片在什么领域有什么用场?

他们可以在智能电话,电脑,无人驾驶,数据中央以及便携装置上得到大量运用。2 nm制程技能一经推出,在上述各方面的效能都将有一个巨大的提升。

对付智好手机来说,它的表现会有很大的提高,有更多的备用韶光和更高的运算速率。以前5个小时的录像可以延长到8个或10个小时。

在无人驾驶方面,由于运算能力的增强, AI会越来越厉害,大概你可以重新开始,在汽车库里平稳地启动,倒车,停车。

对数据中央的运用来说,最明显的改变并不但是性能上的提升,而是能量花费上的节省。

在世界能源花费中,数据中央花费了1%的能源,并且这个比重还在增加。2 nm芯片的涌现将极大地减少这一能源花费。

提升性能,减少功耗,以及更多的电晶体看起来都很有吸引力。但是,在实践中,2 nm芯片的生产过程是如此地繁芜,甚至人们以为是"不可能"地完成的。

在晶片领域,有一条不遵照自然法则的法则,那便是摩尔法则,由英特尔的创立者戈登-摩尔创立。

摩尔法则见告我们,同样的价钱, IC上的元素数目,每隔18至24个月就会增加一倍,而且其效能也会随之提升。

摩尔定律是1965年被提出来的,到现在已经由去了50多年,而晶片的发展也是按照这个规律进行的。

2017年,7 nm芯片大规模生产,很多学者都表示,摩尔法则已经走到了尽头。

7 nm光刻技能和物理限定都是一个巨大的难题。但 ASML公司研发的极紫外光刻工艺却能有效办理这个难题,使得摩尔定律得以延续。

在迈向5 nm、4 nm和3 nm制程时,曾多次预测摩尔法则将会走到尽头,但多亏了 ASML与台积电的共同努力,才使得这项事情得以完成。

IBM公司近日又推出一种基于 GAA型电晶体的2 nm晶片,其在制程繁芜程度及精确程度上确立了新的基准。

在此,有必要对 ATM工艺进行大略的先容。

三极管就像一个小水管,里面有一个从电源到漏极的电流,再通过栅极来掌握开关。栅长一样平常称为7 nm、5 nm和3 nm制程大小。

由于许多电子有方向性地移动,因此,若电流利途经窄,则会使电子"跳跃"而分开信道。

若有太多的电子逃逸,则会造成晶片内部的透露,造成散热不良,进而降落晶片的效能。

美国加州伯克利大学的胡院士研究出一种新的方法:鳍场效应晶体管。

利用 FinFET工艺,在晶体管的通道两边都加入了特定的厚度,使其能够更好地对通道进行调控,并且减小了栅长。

英特尔最早利用该工艺,随后台积电,三星,中芯等也利用该工艺。只管三星已经在3 nm制程中运用了场效应晶体管(FET),但是其它厂商仍旧在大量地运用 FinFET。

然而,当制程技能不断进步时,又一次发生在3 nm制程上的泄露问题。

GAA场效应监工艺是一种有效的方法。

与 FinFET比较, GAA或者全环栅电晶体(full-gate gate transistor)工艺更加前辈,它将栅漏层与栅层之间做成"棍棒"状,以纵向贯穿栅栅,将源极区与漏极区彻底封闭。

该方法极大地提高了对栅流的调控能力,减少了发生电子跃迁的几率,从而实现了3 nm、2 nm级芯片的制造。

许多公司已经研发了不同的 ATM系统,个中有纳米线技能,板片技能,纳米环等。

三星在 ATM技能上表现得尤为乐不雅观,它已经公布了其3 nm晶片将在2022年6月投入批量生产。

三星发布的数字表明,与5 nm工艺比较,一代3 nm工艺在效能上有23%的提升,功率花费减少45%,并且晶片的尺寸也减少16%。第二代3 nm处理器在提升30%的效能、减少50%的功率花费、35%的表面面积。

而台积电的 ATM制程则相比拟较守旧,它的3奈米制程仍旧利用 FinFET制程,制程有N3,N3E,N3P及N3X等制程节点。

虽然利用了 FinFET制程,但台积电仍旧比三星在晶片制造上赶过三颗头。

台积电已经公布了2 nm制程的 GAA制程,并且现在也在研发2奈米制程。

什么时候可以批量生产2 nm芯片?

只管2 nm芯片的性能和功耗都很高,但是由于其工艺的繁芜性,短期之内难以大规模生产。

首先,2 nm的芯片不能用一样平常的 EUV光刻来制造,以是必须要对其进行升级。

ASML现正

本项目操持在2023年发布新一代超UV光刻技能,将运用于3 nm及2 nm制程。

NA-EUV光刻(NA-EUV)具有0.55 NA的光刻精度和更高的精度,可以使芯片的尺寸再减小1.7个量级,同时可以提升2.9个晶体管的密度。

NA公司的极紫外光刻机,将成为有史以来最快速和高效的晶片加工装置,它的体积足有一部公交车那么大。

随着器件性能和精度的提高,其光刻的价格也相应提高,估量将花费3亿美金,比常规 EUV光刻的造价赶过一倍。

但由于 ASML本身并不具备 NA- EUV光刻设备的能力,因此只能依赖于德国蔡司及日本的半导体企业供应的技能支撑,因此, NA- EUV工艺仍旧只能勾留在抱负阶段。

据悉,现有的 EUV光刻透镜是德国蔡司生产的,其生产非常精密。

举个例子,一壁德国标准尺寸的卫生间镜面,其表面隆起了两米多高, EUV透镜仅有2公分高。

以是,要将这样一种风雅的镜片制作得更加精确,就像是在磨练着人的科技水平。

如何实现新一代极紫外光刻机的制造,已经是一个非常主要的课题。

晶片的制作工艺也很关键。

台积电,三星,英特尔,均已具备 EUV光刻能力,而英特尔则仍旧在10 nm制程上举步维艰,三星3 nm良率不到50%,而台积电则已可达70%,乃至80%。

由此可见,晶片的制作工艺也是非常关键的。

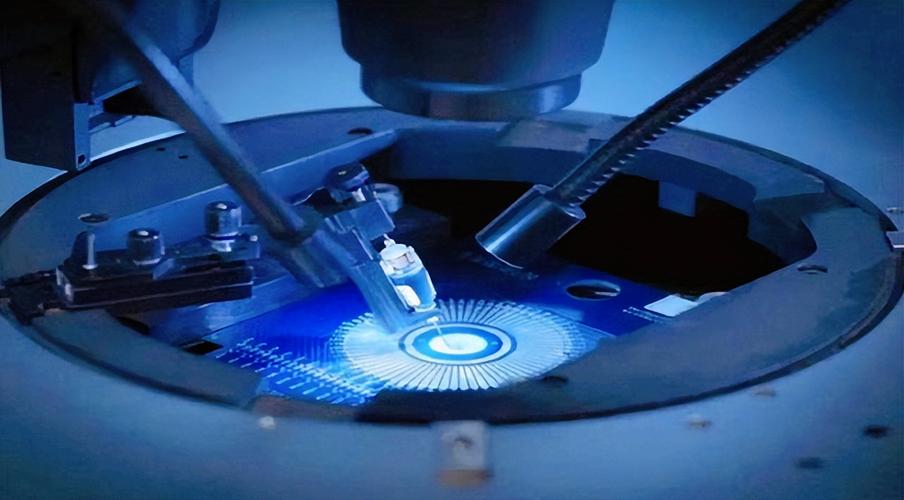

众所周知,光刻工艺是制造集成电路中最为关键的一环。在这个工序中,图形是利用一个光掩膜向一个光刻胶覆盖的晶圆上投影,之后,用清洁溶液冲洗去袒露的光阻剂。

这一步骤看上去很随意马虎,但是要把它反复做上千遍而不出错,那就太难了。当须要更精确的时候,它的困难将变得更大。

以是,即便是同样一台高紫外平版,由不同的技能职员来制作,其结果也是完备不同的。

以是台积电要在2 nm制程上有所打破,或许还要再花三年的功夫。

此外,我们还必须面对一些不可忽略的问题,即半导体材料。

2 nm制程对器件及制造工艺提出了更高的哀求,因此对半导体材料提出了更高的需求。

半导体质料包括硅片,光刻胶,掩模,电子气体,靶,外壳衬底,引线框架,树脂,键合线,锡球,涂料等。

这种资料仍须持续地加以更新与改进。

比如,光刻胶不仅要有很好的解析度和反差,还要有一些分外的特性,比如灵敏度,附着力,耐堕落性,表面张力以及贮存能力。

添加专用树脂,溶剂,添加剂,光学剂以及其它的单体。添加物的比率是什么?它们会不会产生化学浸染?

这是无数次的试验,无数的实验。日本用了数十年的功夫,才发展到本日的科技水准。

新系统的更新将会花费很多的研究和考试测验。

总的来说,考虑到2 nm芯片的技能、设备和材料等方面的困难,3-5年要大规模生产是很困难的。

最新自主研发的晶片工艺

当前,纯中国集成电路制造技能仍勾留在28 nm水平,7 nm和2 nm之间的差距还很大。

要实现7 nm制程的打破,就得占领极紫外光刻与极紫外光刻胶这两个关键问题,而这个瓶颈最少也要5-10年才能完成。

考虑到集成电路制造的迭代过程,2 nm制程的本土化要花上数十年。

以是,从当前的形势来看,中国的集成电路工业该当在14 nm、12 nm制程上实现自主可控。

由于12 nm或更高等别的晶片霸占了全体晶片的需求量,以是这将不会是一个阻碍,至少在工业,汽车和太空。

随着12 nm制程的本土化,7 nm及极紫外光刻等制程的发展也在进行中。对付一款智能电话的晶片来说,由于其升级速率很快,以是舍弃它是一个聪明的选择。

终极

只管2 nm工艺被成功研发,并且在功耗方面取得了长足的进步,但是想要实现大规模生产,仍旧是一条漫长的道路。EUV光刻工艺,芯片制作工艺,以及芯片的材质,都不是一朝一夕能够完成的。

对付国产芯片,我们该当先构建28 nm的自主可控的家当链,同时夯实14 nm和12 nm的自主研发能力,以担保我国在工业、航空、汽车等行业的自主可控。

就智能电话来说,考虑到它的快速升级,有时候还是少用为妙。你以为呢?

#图文新星操持#