(重庆邮电大学,重庆400065)

:在利用Digital Signal Processor (DSP)芯片进行数字旗子暗记处理时,由于数据量大,线程较多,常日采取多片DSP协同处理。本文旨在研究DSP间数据和信息传输的实现,并以三片TI的 TMS320C6474芯片为例,基于SRIO协议,设计一种传输架构,实现了DSP间的数据传输。终极实现DSP间2.520 Gb/s的数据传输速率,为理论值的50.40%,但如果撤除线程调度和DSP间同步所用韶光,其SRIO接口的数据传输速率可达到3.886 Gb/s,为理论值的77.72%。该设计具有较大的通用性,对其他同类型的芯片间的数据传输设计具有极大的参考性。

:多核;DSP;SRIO;DSP间数据传输

:TP368.2文献标识码:ADOI: 10.19358/j.issn.1674-7720.2017.04.011

引用格式:魏智伟.多核DSP间基于SRIO数据传输的设计与实现[J].微型机与运用,2017,36(4):36-39.

0弁言

伴随着DSP所需处理的数据量和开拓的功能模块的增多,单片DSP运行的进程数增多,负载过大,系统越来越难以知足实时处理的哀求。如果选择多片DSP协同运行,不仅可以减少单片DSP的负载,提高系统的处理性能和相应速率,从而达到实时处理的哀求,还能进行更多功能模块的开拓,对付数字旗子暗记处理系统来说定是有益的。但多片DSP进行协同运行时,DSP间须要设计完成数据交互的功能。本文依据Rapid IO协议的标准,结合TI的TMS320C6474芯片的特点,在Digital Signal Processor_Basic Input Output System(DSP_BIOS)的开拓平台上,设计和实现了多核DSP间的数据传输。本文首先先容了该设计所需的各个功能模块,然后阐述整体设计的流程和详细实现的办法,末了对DSP间数据传输性能进行了测试。

1DSP间通信所需功能模块简介

1.1Mailbox(邮箱)

基于DSP_BIOS的开拓平台,TI供应了一个Mailbox(MBX)模块,开拓者可以通过TI的用户接口函数来进行管理,利用该模块。Mailbox用来图1用Mailbox实现线程间通信实现DSP内部的同一个核内的不同进程(TSK)间的相互通信[1]。MBX_post用于发送端,MBX_pend用于吸收端,实在现示例如图1所示。

1.2Semaphore(旗子暗记通信)

TI供应了一个Semaphore[2]模块,该模块可以用于管理对共享资源的访问。其访问模式有三种:直接模式,间接模式,综合模式。本文采取的是直接模式:读取寄存器DIRECT的值,如果DIRECT的值为1,则表明该共享资源可用,许可访问,并得到该旗子暗记量;反之如果DIRECT的值为0,则表明该共享资源正在被其他进程访问。当对共享资源操作完成后,须要对DIRECT写1,以开释对该资源利用的权利。

1.3Rapid IO

1.3.1Rapid IO简介

Rapid IO协议是一个开放的点对点分组交流标准,是面向嵌入式系统开拓提出的高可靠、高性能、基于包交流的互联技能[3],传输速率能达到1 Gb/s以上。其最紧张的特点包括:(1)有缺点检测机制; (2)低负载高带宽;(3)引脚少[4]。

1.3.2Rapid IO架构

SRIO总线是一种开放式的基于包交流的高速串行标准总线[5],Rapid IO协议采取三层分级体系构造:

(1)逻辑层:规定了端点间传输的协议和包格式。

(2)传输层:定义了在系统中传输的包所需的路由信息。

(3)物理层:包含了硬件级接口的信息,比如电气特性、缺点数据管理、基本数据流掌握。

1.3.3SRIO包构造

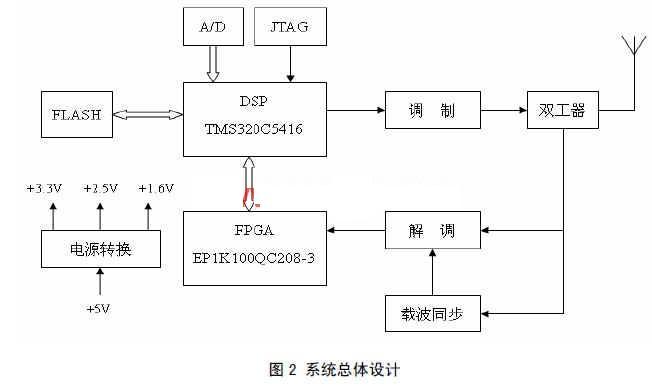

在SRIO的包构造中,包的种类有很多,紧张用到的为数据包和门铃包。数据包用于在源地址和目的地址间进行数据传输,其构造如图2所示。门铃包紧张用于触发相应的中断,关照相应DSP的某个核进入中断相应函数,实行相应的操作,但门铃包不携带数据信息,其门铃包的构造如图3所示。

个中包构造各个段的含义是:AckID:交流构造期间将利用掌握符号来确认是哪一个包;Prio:表明该包的优先级;tt:指定Device ID是用8 bit或16 bit表示;fftyp:表示包的类型;destID:包传送的目的地址ID;sourceID:发送包的源地址ID;CRC:包构造的校验保护;Info:门铃中断触发掌握。

1.3.4Rapid IO包传输

包构造(packets)是SRIO传输两个端点之间传输的单位,其传输是基于要求包和相应包。图4发送端和吸收端分包交互流程

其一次数据传输流程为:发送发起端产生一个要求包给吸收端,吸收端收到后返还一个相应包给发送发起端[6]。图4表明了发送端和吸收真个包交互流程。

2DSP间通信的设计与实现

2.1资源的配置

2.1.1SRIO端口连接

每片TMS320C6474芯片有两个SRIO实体端口(分别命名为Port0,Port1),将其分别与其余两片DSP的任意一端口相连,如图5所示。通过该连接,可以担保任意一片DSP能与其他两片DSP直接连接。当发送端DSP和吸收端DSP都已确定时,相应SRIO端口的选择也就确定了。

2.1.2DDR共享内存的分配与管理

每块DSP上都外挂一片DDR存储器。DSP的任意一个核Core0、Core1、Core2都能访问该存储器(TMS320C6474 为三核处理器,将三个核依次命名为Core0、Core1、Core2)。在DSP0,DSP1,DSP2的DDR存储器里指定一块内存用于存储DSP间任务调度的信息(以下称该段内存为共享调度内存),如图5所示。每片DSP上分配的公共调度内存的方案与管理如图6所示。对每个DSP三个核的内存分别分配一个Semaphore(旗子暗记通信)用于管理对吸收端DSP的共享调度内存的访问。

2.1.3中断的分配与利用

当发送端将发送给吸收端后,关照吸收端相应的核来处理该。这次设计的方案是通过SRIO口传输门铃包(DOOEBELL Packet),门铃包携带吸收端相应核的信息, 触发吸收端相应核的中断。

当发送端发送DOORBELL包时,此包被用作初始化CPU中断,包构造中INFO段表明干系DOORBELL寄存器的干系中断位被设置,如图3所示。一个DSP有4个DOOEBELL寄存器,每个寄存器有16 bit,有64个中断源产生中断。通过ICR(Interrupt Condition Routing)寄存器,可以将每位路由给任意核。本文将DOORBELL寄存器的最低的三位分别分配给DSP的三个核(Core0,Core1,Core2)。即若DOOEBELL的最低位为1,则DSP的Coer0相应傍边止。

每个DSP都有两个SRIO口,如图5所示,前面已经将DSP互连的SRIO口进行了编号(0,1),按照SRIO口的编号(0,1)分别分配以DOOEBELL 0和DOOEBELL 1寄存器,DOOEBELL 0和DOORBELL 1寄存器又分别映射到SRIO的两个中断通道(71~RapidIO Interrupt(2n),72~ RapidIO Interrupt(2n+1)),将此两个中断分别分配给两个SRIO口,使之分别相应SRIO口的中断。该Rapid IO Interrupt紧张用于判断发送真个DSP的编号。如图7所示,吸收端为DSP0,若中断通道71~RIOINT被触发,则判断发送端为DSP1,若中断通道72~RIOINT被触发,则判断发送端为DSP2。

通过以上中断的配置,可以担保发送真个任意DSP都能通过DOOEBELL包关照到吸收真个任意核,同时吸收端也能判断出发送端为哪个DSP。

2.2设计思路与详细实现

2.2.1设计思路

实现多核DSP间的数据交互紧张完成两方面的事情:(1)实现数据的搬移;(2)关照吸收真个DSP数据存储的位置和长度。实在现流程图如图8所示。

2.2.2详细实现流程

(1)SRIO初始化。①SRIO电源模块的初始化:对SRIO干系的模块供应电源。②SRIO的SERDES模块初始化:配置PLL,配置RX0、TX0和TX1、TX1的传输通道,配置SRIO的端口0和1。③检讨SRIO口是否配置完成。

(2)选择SRIO端口。根据发送真个DSP和吸收真个DSP决定选择SRIO口,即选择数据传输的物理链路。

(3)获取向吸收真个共享调度内存写入的旗子暗记量。通过Semaphore(旗子暗记通信)管理不同发送端对吸收端DSP的共享调度内存的访问,若该旗子暗记量被占用,则一贯等待该旗子暗记被开释。

(4)通过SRIO口传输数据包。配置Load/Store Register完成包的组成。其关键配置有:配置LSUn_REG2中的DSP Address,完成待传输数据(payload)的源地址和目的地址的配置;配置LSUn_REG3中的Byte_count完成待传输数据的长度;配置LSUn_REG5中的Packet Type完成包种类的配置。配置完成后,使能传输。其Load/Store Register相应字段的配置会映射到数据包中,待传输数据通过SRIO口存到了公共调度内存中。

(5)通过SRIO口传输DOOEBELL包:该包用于关照吸收端DSP的相应核的共享调度内存有待处理。通过对LSUn_REG5的Drbll Info段进行配置,使之映射到DOORBELLn_ICRR寄存器中,本文将DOOEBELLn_ICRR的第0位、第1位和第2位,通过ICR(Interrupt Condition Routing)寄存器使之分别路由到核0、核1、核2。则通过DOOEBELL包就能在吸收端DSP相应的核上产生中断。第(2)步已经得到了相应的SRIO的端口号,通过SRIO端口号为0或1决定DOORBELLn_ICRR为DOORBELL0_ICRR或DOORBELL1_ICRR。该DOORBELL0_ICRR和DOORBELL1_ICRR分别对应着吸收端DSP相应核上的两个SRIO_INT中断。在2.1.3节中已经先容,借此来判断发送真个DSP的编号。由此吸收端能判断出数据在共享调度内存中的存储位置,如图9所示。以发送端为DSP0_Core0、吸收端为DSP1_Core1为例,其应存储在DSP1的共享内存中的DSP0、Core1段。

(6)吸收端DSP相应的核读取共享调度内存的数据,解析收到的并通过Mailbox(邮箱)模块,在吸收端DSP相应的核内进行核内线程调度,触发相应的任务。

(7)吸收端DSP实行完相应的任务后,给发送端返回相应的数据,发送端DSP和Core的编号都会在传输的过程中保存,以是吸收端往发送端返回时按照前几个步骤的逆过程进行数据传输。

通过以上几个步骤后,多核DSP间的数据传输已经实现。

3数据传输测试

本文对多核DSP间的数据传输进行测试[7],SRIO口的事情速率设置为3.125 Gb/s,经由物理层8B/10B编码,数据包实际传输速率为2.5 Gb/s,利用两个1x通道,理论传输数据为5 Gb/s。

数据传输精确性的测试:从DSP0Core0发送2k次的数据给DSP1Core2,DSP1Core2收到数据后将数据转发给DSP2Core1,DSP2Core1收到数据后再发送回DSP0Core0,DSP0Core0末了将收到的数据与最初发送的数据进行比拟,检测数据有无缺点。本文采取每隔1 s发送一次数据,测试一星期未创造出错。

传输性能的测试:任意选取两片DSP的任意核进行不同数据长度的回环测试。例如数据从DSP1发送至DSP2,DSP2收到数据后将数据返回给DSP1。从DSP1刚开始发送数据和刚吸收完数据后分别利用_itoll(TSCH,TSCL)函数获取CPU的Cycle值,打算两次值之差,即可测出速率[8]。

通过数据剖析可以得出,数据的传输速率为2.520 Gb/s旁边,为理论值的50.4%。但传输长度为64 B时,传输的数据较少,可近似为线程调度和DSP间同步所需的韶光,若将传输32 000 B的韶光减去传输64 B韶光(线程调度和DSP间同步所需韶光),再打算传输速率的值为3.886 Gb/s,为理论值的77.72%。由于数据包的组包和解包,以及DDR上读取数据的开销等,实际数据会小于理论值。

4结束语

本文在DSP_BIOS操作平台上,基于Rapid IO协议,实现了多核DSP间的数据传输。这次设计不仅适用于2个多核DSP间的数据传输,同时也适用于3个乃至3个以上多核DSP间的数据传输。该架构能协同多个DSP进行大量的数据处理,相对减少了单个DSP处理的时延和包袱,提高了系统的处理能力和相应速率,对数字旗子暗记处理系统的发展具有一定的推动浸染。

参考文献

[1] Texas Instruments Group. TMS320 DSP/BIOS v5.42 User’s Guide (SPRU4231) [EB/OL].(2013-08-xx)[2016-09-20]http://www.ti.com.

[2] Texas Instruments Group. TMS320C6474 DSP Semaphore User’s Guide (SPRUG14)[EB/OL].(2016-09-20)[200810xx]http://www.ti.com.

[3] 陈婷,岳强,汪洋.FPGA和DSP间基于SRIO的高速通信系统设计[J].单片机与嵌入式系统运用,2016(3):37-40.

[4] Texas Instruments Group. TMS320C6474 DSP Serial Rapid IO(SRIO) User’s Guide (SPRUG230) [EB/OL].(2011-10-xx)[20160920]http://www.ti.com.

[5] 王磊,王辉球.基于高速串行总线SRIO的数据传输[J].电子制作,2015(5):16-18.

[6] 黄克武,吴海洲.基于TMS320C6455的高速SRIO接口设计[J].电子丈量技能,2008,31(9) :143147.

[7] 冯超,张涛.TMS320C6678高速串行接口的传输性能研究[J].单片机与嵌入式系统运用,2015,15(11):52-55.

[8] 侯普.基于TI KeyStoneⅡ多核DSP技能的研究与利用LTEA基带板处理板设计与实现[D].北京:北京邮电大学,2015.