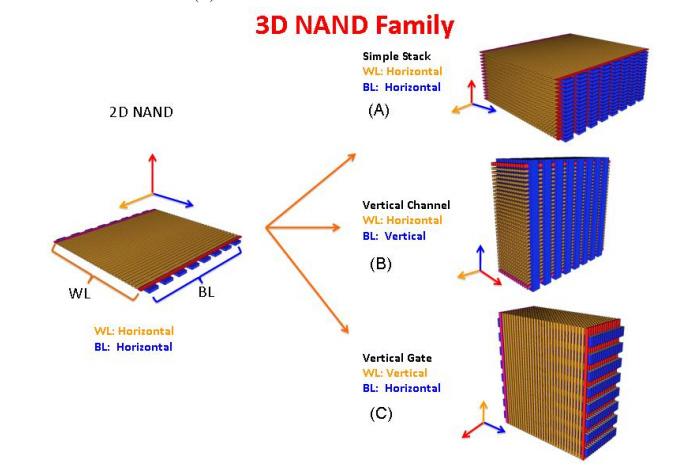

《3D NAND先容》

NAND分为2D和3D,有了2D NAND,为什么要升级到3D呢?

2D NAND与3D NAND的存储单元的构造比拟

如图:

在2D NAND构造中:

掌握栅(Control Gate):位于顶部,掌握下面的浮动栅。通过掌握栅的电压,可以掌握电子是否可以进入或从浮动栅中离开。

浮动栅(Floating Gate):位于掌握栅下方,被绝缘层包裹,用于存储电子。电子流入或从浮动栅中离开来表示数据的1和0。

Single-Si Channel:这是连接源极(S)和漏极(D)的硅沟道。电子通过这个通道从源极流向漏极,根据浮动栅的电荷状态来掌握这个流动,从而读取存储的信息。

而对付3D NAND,

掌握栅(Control Gate):3D NAND的掌握栅是环抱着存储柱的立体构造。

Poly-Si Channel:与2D NAND的单晶硅通道不同,3D NAND中的通道是垂直构建的,并由多晶硅材料构成,形成一个立体的存储柱。

氮化硅(Nitride):3D NAND利用电荷陷阱存储电子。电子被存储在氮化硅中,氮化硅是包裹在多晶硅沟道周围,代替了2D NAND中的浮动栅。这种电荷陷阱层使NAND具有非易失落性的数据存储能力。

我们再进一步解剖3D-NAND的构造,如图:

Silicon wafer base layer:这是3D NAND构造的根本,即硅片。

Silicon bit cell gates:是掌握电子流动的门构造,它们决定了是否许可电子进入或离开Silicon channel,从而实现数据的存储和读取。

Silicon dioxide gate dielectric:位于掌握栅和Silicon channel之间的绝缘层,其功能是保持掌握栅和Silicon channel之间的电气隔离。

Silicon channel:其内部流动的电子被掌握栅的电压掌握,用以存储信息。

Silicon dioxide tunnel dielectric:它使电子在写入操作中通过隧道效应流入到Silicon nitride charge trap,以及在擦除操作中从Silicon nitride charge trap中移除。

3D NAND的上风?

3D NAND的构造极大地提高了存储密度,并减少了晶体管间的滋扰,从而提高了数据的读写速率,减少了功耗,延长了利用寿命。

欢迎加入我的半导系统编制造知识社区,答疑解惑,上千个半导体行业资料共享,内容比文章丰富很多很多,适宜快速提升个人能力,先容如下:

《欢迎加入作者的芯片知识社区!

》