内容:回顾FPGA逻辑部分Verilog实验---按键检测(脉冲边沿检测法);

来源:实际得出;

浸染:回顾FPGA逻辑部分Verilog实验--按键检测(脉冲边沿检测法);

仿真环境:Quartus II 11.0;

日期:2019-04-23;

=====================分割线========================

立题详解:

本次回顾FPGA逻辑部分Verilog实验--按键检测(脉冲边沿检测法),利用“FPGA芯片”为“EP4CE6E22C8”,价格约“15.00RMB/PCS”,“LEs数目”约为“6272”;

本次先容为“与非门”,代码实测可用,简介如下:

i)、“开拓环境”:环境为“Quartus II 11.0”;

ii)、FPGA芯片:芯片为“EP4CE6E22C8”,价格约“15.00RMB/PCS”,“LEs数目”约为“6272”;

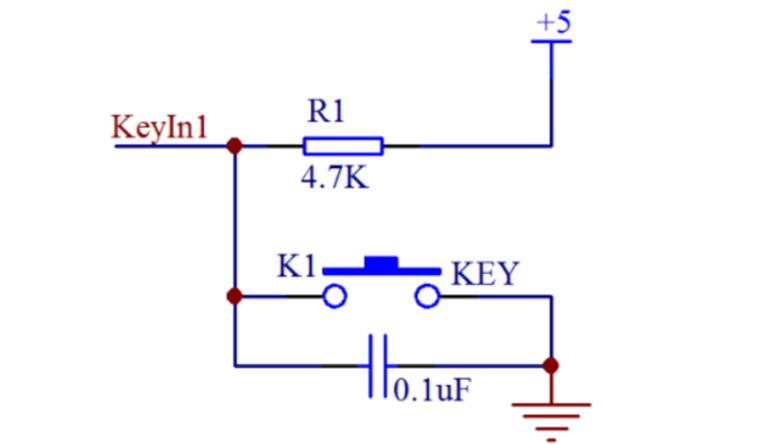

1、“按键实验”实际先容

对“按键检测”代码而言,有2种方法(FPGA为硬件描述,无直接的延时描述):

i)、“普通检测法”:直接读取“输入按键”的电平状态,很难消抖,误判概率很高;

ii)、“脉冲边沿检测法”:读取“输入按键”的电平状态,并添加“延时消抖剖断”,可有效减少误触发的概率;

本次利用“脉冲边沿检测法”来做;

2、脉冲边沿检测法-代码

对“脉冲边沿检测法”而言,其核心分为“4点”:

i)、“第一次检测”:即“第一次涌现边沿变革”,此时会获取“第一次触发值”;

ii)、“中间消抖”:即从“第一次涌现边沿变革”开始,进行延时,建议时长为“20ms旁边”;

iii)、“第二次检测”:即延时后,检测“边沿变革是否依旧存在”,并所存“键值”,个中的“键值”为“非零值”;

iv)、“电平实行部分”:即“得到键值”后的动作函数;

首先,第一次检测代码:

reg[1:0] key_rst;

reg[1:0] key_rst_r;

wire[1:0] key_an;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)key_rst <= 2'b11;

else

key_rst <= {key2_n,key1_n};

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)key_rst_r <= 2'b11;

else

key_rst_r <= key_rst;

end

assign key_an = key_rst_r & (~key_rst);

然后,延时期码:

reg[20:0] delay_20ms;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)delay_20ms <= 21'd0;

else if(key_an)

delay_20ms <= 21'd0;

else

delay_20ms <= delay_20ms + 1;

end

然后,所存代码:

reg[1:0] low_sw;

reg[1:0] low_sw_r;

wire[1:0] led_ctrl;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)low_sw <= 2'b11;

else if(delay_20ms == 21'hffff)

low_sw <= {key2_n,key1_n};

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)low_sw_r <= 2'b11;

else

low_sw_r <= low_sw;

end

assign led_ctrl = low_sw_r & (~low_sw);

特殊把稳:“delay_20ms == 21'hffff”的“延时剖断”,如下所示:

末了,动作代码:

reg d1;

reg d2;

always @(posedge clk or negedge rst_n)

if(!rst_n) begin

d1 <= 1'b0;

d2 <= 1'b0;

end

else begin

if(led_ctrl[0]) d1 <= ~d1;

if(led_ctrl[1]) d2 <= ~d2;

end

assign led1 = d1 ? 1'b1:1'b0;

assign led2 = d2 ? 1'b1:1'b0;

把稳:“ d1 <= ~d1”为“取反”;“led1 = d1 ? 1'b1:1'b0”为“掌握输出”;

如下图所示:

3、脉冲边沿检测法-RTL级和引脚分配

RTL级截图如下:

引脚分配如下: