什么是高下拉电阻?

上拉电阻和下拉电阻是根据电阻不同的利用场景来定义的,并不存在上拉和下拉这两种实体的电阻,实质上是电阻。类似的还有去耦合电容和耦合电容,也是根据运用处所来取名,不存在实体的电容,实质是电容。

高下拉电阻事理

上拉电阻:在某旗子暗记线上,通过电阻与一个固定的高电平VCC相接,使其电压在空闲状态保持在VCC电平,此时电阻被称为上拉电阻。也便是说把一个旗子暗记通过一个电阻接到电源(VCC)。

如下图所示:电阻R12将KEY1网络标识上拉到高电平,在按键S2没有按下的情形下KEY1将被胁迫在高电平,从而避免了引脚悬空而引起的误动作。

上拉电阻图

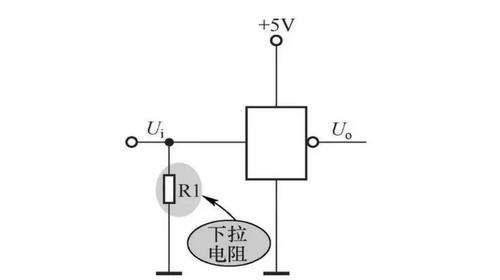

下拉电阻:在某旗子暗记线上,通过电阻与一个固定的高电平VCC相接,使其电压在空闲状态保持在VCC电平,此时电阻被称为上拉电阻。也便是旗子暗记接到地(GND)。

下拉电阻图

电阻R29将DIR网络标识下拉到低电平,在光耦没有导通的情形下DIR将被胁迫在低电平,从而避免了引脚悬空而引起的误动作。

“强上拉”、“弱上拉”是什么?

强弱只是上拉电阻的阻值不一样而已,没有什么严格的区分。例如50Ω上拉,则一样平常称为强上拉;100kΩ上拉则称为弱上拉。

“强下拉”、“弱下拉”也是一样的,强下拉电阻的极度便是0欧姆电阻,或者是将旗子暗记线直接与电源或地相来连接。

高下拉电阻的浸染

1、坚持输入管脚是一个稳定态

芯片的管脚有三个类型,输出(Output,简称O)、输入(Input,简称I)和输入输出(Input/Output,简称I/O)。芯片的输入管脚,输入的状态有三个:高电平、低电平、和高阻状态。当输入是高阻,即输入管脚悬空,很可能造成输入的结果是不稳定态,引起输出振荡。有些运用处所不肯望涌现高阻状态,可以通过上拉电阻或下拉电阻的办法使这个输入管脚处于稳定状态。

2、提高电压准位(电平标准匹配)

当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS电路的最低高电平(一样平常为3.5V),这时就须要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的高电平值。

TTL电路

3、加大输出引脚的驱动能力

芯片的输出管脚本身并不是OC、OD,但是有时我们也会增加一个上拉电阻或下拉电阻,通过上拉或下拉来增加或减小驱动电流。

例如,一个单片机的I/O口内部有一个几十kΩ,最大输出电流也便是250μA,因此当我们增加一个上拉电阻时,可以形成和内部上拉电阻并联结构,增加高电平时电流的输出能力。在负载增大时,仍旧能够保持足够的电压。

4、N/A引脚(没有连接的引脚)防静电、防滋扰

在CMOS芯片上,为了防止静电造成破坏,不用的引脚不能悬空,一样平常接上拉电阻降落输入阻抗,供应泄荷通路。同时引脚悬空就比较随意马虎吸收外界的电磁滋扰。芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入旗子暗记的噪声容限,增强抗滋扰能力。长线传输中,电阻不匹配随意马虎引起反射波滋扰,加高下拉电阻是电阻匹配,有效地抑制反射波滋扰。提高总线的抗电磁滋扰能力,管脚悬空就比较随意马虎受外界的电磁滋扰。

5、电阻匹配

抑制反射波滋扰,长线传输中电阻不匹配随意马虎引起反射波滋扰,加高下拉电阻使电阻匹配,能有效地抑制反射波滋扰。

6、预设空间状态/默认电位

在一些CMOS输入端接上拉或下拉电阻是为了预设默认电位。当不用这些引脚时,这些输入端下拉接低电平或上拉接高电平。在I2C等总线上空闲时的状态是由高下拉电阻得到的。

7、提高芯片输入旗子暗记的噪声容限

输入端如果是高阻状态,或高阻抗输入端处于悬空状态,此时须要加上上拉或下拉电阻,以免受到随机电平的影响,进而影响电路事情。同样,如果输出端处于被动状态,须要加上拉或下拉电阻,如输出端仅仅是一个三极管的集电极,从而提高芯片输入旗子暗记的噪声容限,增强抗滋扰能力。

在BJT晶体三极管的基极度,上拉电阻和下拉电阻也起着至关主要的浸染。在三极管的电路运用中,串接在基极上的电阻起限定基级电流的浸染,如下图中的R2所示。

三极管的电路

如下图中的R5所示,上拉电阻使三极管基极的输入电平在默认情形下是高电平输入,当CPU有低电平旗子暗记输出时,外围电路相应,下拉电阻使晶体管的基极输入在默认情形下拉到低电平,如下图中的R6所示。

下拉电阻运用

高下拉电阻的阻值选择

电路设计中,一样平常阻值大小都是凭借履历选取的。上拉电阻阻值有4.7k欧姆,10k欧姆等。但详细的还是要从以下方面考虑:

1、功耗

上拉电阻和电源相连接,下拉电阻和GND相连接,在对电阻进行选型时,须要考虑到电阻自身带来的损耗。比如在按键电路中,电阻取10K可以知足条件,取20K也可以知足条件。但是明显电阻取20k时,电阻花费的能量会更低。在对待机有需求的电路中,须要严格掌握高下拉电阻的取值。

2、驱动能力

驱动能力的大小和供应的电流有关系。比如在OC门和OD门电路中,上拉电阻取太大,在输出高电平时,无法为后级供应较大的电流。如下图所示,LED正常事情时须要5~10mA电流,如果电阻取太大,LED灯无法点亮,因此需结合LED灯的电流和电压来选取上拉电阻。

上拉电阻运用图

3、旗子暗记速率

对付高速电路,过大的上拉电阻可能变平缓。须要电阻与电路寄生电容形成RC滤波电路,影响旗子暗记的高频分量的传输。

4、驱动能力与功耗平衡

以上拉电阻为例,一样平常地说,上拉电阻越小,驱动能力越强,但功耗越大,设计时应把稳两者之间的均衡。

5、下级电路的驱动需求

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路供应足够的电流。

6、高低电平的设定

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出精确的电平。以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

7、频率特性

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。上拉电阻的设定应考虑电路在这方面的需求。

8、阻值打算

高下拉电阻阻值怎么打算?以上拉电阻为例,最大值:为确保高电平时输出有效,上拉电阻要明显小于负载的阻抗。若上拉电阻过大,会导致输出的高电平不敷。最小值:不超过场效应管的额定电流(或三极管的饱和电流)。

算出最大和最小值后,选取中间值就可以了。但是,如果负载电流较大,低电平哀求很严格,那么就要选靠近最小值的上拉电阻。如果考虑尽可能的低功耗,那么就选用靠近最大值的上拉电阻。

上拉电阻怎么运用?

1、用在OC/OD门

对付OC(Open Collector,集电极开路)、OD(Open Drain,漏极开路)电路上拉电阻的功能紧张是为集电极开路输出型电路供应输出电流利道。有些芯片他们的一些输出管脚,集成了三极管或MOSFET,但是没有集成上拉电阻到VCC。范例的OC电路如图31.6所示。以是,这些管脚实在便是一个集电极,而且是个开路,以是就称为OC。按照我们先容的三极管的外围电路,这个上拉电阻是必须的内容,我们在事理图中在OC、OD电路放置的上拉电阻,原来便是让电路功能完全的必须内容。

集电极开路电路

OC或OD的由来,是用于设计一种“线与”电路。两个或多个输出旗子暗记连接在一起可以实现逻辑“与”的功能。如图31.7所示,两个输入只要有个中一个输入为低电平,就可以让输出为低电平,两个输入都是高电平时,输出才为高电平。

两个OC电路实现“线与”

2、用在按键电路上

按键电路的事情事理是当按键未被按下和按下时电平取反,MCU通过检测到该管脚的旗子暗记电平被取反了,判断按键是否被按下。事理图如下:

按键电路

当按键未被按下时,此时MCU的IO口检测到高电平;当按键被按下时,此时检测到低电平,上拉电阻是为了担保按键未被按下时处于一个固定的高电平。

3、三极管实现电平转换电路的外围电阻

首先要理解三极管的基本事理,三极管属于电流掌握电流型元件,与MOS管不同,MOS管属于电压掌握电压型元件。三极管有三个事情区:截止区、放大区和饱和区。以NPN三极管为例,BE之间那个箭头很像一个二极管,实在BE之间便是一个二极管,BE的压差(UBE)约为0.6V旁边(实际大小与元器件的型号有关),当UBE<0.6V时,BE间的等效二极管没有导通,此时的三极管也就处于截止状态;随着BE间的电压上升,三极管进入放大区,三极管处于放大区或饱和区时UBE=0.6V。这时BE的压差不会随着输入的电压变高而连续增加,表示出二极管的特性,保持一个导通电压。

如图所示,输入旗子暗记如果是个3.3V电压旗子暗记,三极管的BE电路等效于一个二极管。我们不会把二极管两端直接接到电压和GND之间,一样平常会串联个电阻,进行电流掌握。

三极管电平转换电路

4、用在I2C总线

一些总线有输出输出接口,实质便是OC或OD的接口。I2C(Inter Integrated Circuit,内部集成电路)总线便是范例的OD输出构造的运用,范例的I2C电路都有上拉电阻,如图所示。

I2C接口的SCL与SDA都是OD输出构造输出,这样的好处是可以作为双向数据总线。OC、OD电路每每是刚刚说的输入输出管脚,然而一些总线的I/O便是一些双向数据的旗子暗记,实在便是把输入和输出短接在一起,然后把输出做成OC或OD。这样处理不单用一根旗子暗记实现了双向数据,既可以输出又可以输入,同时办理了双向数据如果同时发送带来的数据冲突的问题。

I2C电路

一样平常来说,芯片的输出管脚是推挽构造。如果两个芯片的推挽构造输出管脚连接在一起,某一个时候两个芯片同为输出,一个如果输出为高、一个输出为低,则可能涌现短路的征象,事情中称为“总线冲突”,如图所示。用OC、OD电路可以避免短路,所有绝大多数总线都是采取这种办法设计,如I2C、LPC、PCI等总线的输入输出管脚都是这样的管脚类型。当然也有些总线办法,I/O端口不须要外接,是芯片内置了上拉电阻。

总线图

对付I2C总线,总线上有两个芯片或多个芯片,所有芯片的引脚输出什么状态,都不会涌现短路的情形引起数据冲突,合营各自芯片内部的数据识别电路及仲裁系统,双方都可以主动给另一方发送信息。也便是说,任何一方都可以将拉低,不拉低时便是开释总线,总线上为高电平,而不会影响起数据冲突,如下图所示。

I2C总线图

5、用在逻辑IC悬空的管脚

数字逻辑电路中由于内部逻辑门会同时开通和关断,SSN噪声比较一样平常的电路较大,管脚悬空就比较随意马虎受到芯片内部和外界的电磁滋扰,在数字电路中不用的输入脚都要接固定电平,通过推举利用1k电阻接高电平或接地。

6、用在终端匹配上

高下拉电阻常常用在高速电路中,进行终端匹配。由于传输线的阻抗不连续会引起旗子暗记号的反射,导致波形涌现过冲,回沟,振铃等征象。因此,必须在传输上进行源端和终真个匹配。

终端匹配常规来说具有两种类型,并联端接和戴维南端接。

并联端接——在终端并联一个与传输线特色阻抗同等的电阻到VCC或者GND。终端并联端接的优点是旗子暗记能量反射回源端之前,在负载端会肃清掉,缺陷是高下拉电阻会有功耗的产生。

并联端接下拉电阻

并联端接上拉电阻

戴维南端接——戴维南端接也称为分压器端接,采取上拉电阻和下拉电阻同时接在终端上。优点是可以降落终端对源端驱动能力的哀求,缺陷是高下拉电阻都存在功耗。

戴维南端接高下拉电阻

当然,高下拉电阻还有其他很多场合根据芯片的哀求或者是电路的设计须要增加高下拉电阻。比如在电平转换电路中,可以利用上拉电阻进行电平之间的转换。

在单片机驱动类似LED的负载时,利用上拉电电阻可以提高I/O口的驱动能力。在三极管的BE之间增加下拉电阻,可以担保三极管在初试状态下处于稳定关断的状态。

我是李工,而立之年,30岁的身体,00后的心,关注我大家一起聊聊元器件。

图片来源于网络

关于高下拉电阻,大家还有什么疑问?或者有什么好的见地,欢迎大家来评论区留言。