1、问题回答

如上图所示三极管放大电路,直流电源给15V,输入旗子暗记VG1为Vpp=2V,f=100MHz的正弦波,输出端没有放大效果,输出真个波形基本和输入端同等。什么缘故原由?

共有3位小伙伴做了回答,感谢三位的留言,特殊是第一位小伙伴,回答很详细。这个电路失落去放大效果,确实是由于输入波形的频率过高。如果把输入旗子暗记频率降下来,放大效果就出来了。感兴趣的同学,可以自己试一把。原始的仿真工程文件,我已经放在文末。

2、知识点:特色频率fT

细心的小伙伴,可能会问:

①为什么把输入旗子暗记频率降下来,就有放大浸染了呢?

②输入旗子暗记频率高到什么程度才会失落去放大浸染呢?

这都是好问题,存心思考过,才会有这样的问题。

敲黑板,知!

识!

点!

来!

了!

三极管有个参数“特色频率fT”,当晶体事情频率超过一定值时,β值开始低落。当β值低落到1时所对应的频率即为该管的特色频率。在三极管的Datasheet上,一定会标注出来该数值,如下图所示,即为MMBT3904L的fT值,300MHz。

如此,当事情频率f>特色频率fT时,三极管一定失落去放大浸染。细心的小伙伴,可能又会问:③输入旗子暗记频率是100MHz,还远小于fT=300MHz啊,怎么会没有放大浸染?

又是一个好问题!

确实没有超过300MHz,100MHz和300MHz之间差着200MHz呢!

我们不妨看看输入旗子暗记频率在100MHz时的仿真结果。

如上图所示,VF1是输入端旗子暗记波形,100MHz,VF2是输出端旗子暗记波形,也是100MHz。从幅值上看,VF2比VF1轻微大一点点。

如果我们把VF1的频率调度为200MHz,再看下仿真效果,如下图所示。VF2比VF1轻微大一点。

如果我们把VF1的频率调度为300MHz,会若何?再仿真看下……

原文链接:https://www.dianyuan.com/eestar/article-5740.html

运放和三极管组成的恒流源电路剖析

序言

消费电子是指可供消费者日常利用的电子设备,常日具有小巧轻便、操作大略和节能设计等优点。

LED在手机、MP3播放器、游戏机、学习机等的手持产品的LCD背光用的比较多。为了延长LED的利用寿命,LED驱动电源须要具有的恒流输出特性就很主要。

其余,我们的这些消费类电子产品都要进行充电,极大的充电电流对电池也随意马虎形成损伤,以是充电初期基本上都采取恒流充电。

正文

本日跟大家分享一个由运放和三极管组成的恒流源电路。希望对你有帮助。

本文将从以下五个方面对该电路进行阐述:

图1 讲解框图

一、运放和三极管的基本公式

1.1关于运放:

图2 运放

运放的打算过程中基本都会用到虚短和虚断,即:

“虚短”是指在剖析运放处于线性状态时,可以把两输入端视为相同电位,这一特性称为虚假短路,简称虚短。即:

“虚断”是指在剖析运放处于线性状态时,可以把两输入端视为等效断开,这一特性称为虚假开路,简称虚断。即:

1.2关于三极管

图3 三极管电流走向

公式如下:

二、电路简介

这是由运放U1A和三极管Q1及干系阻容元件组成的恒流源电路。

图4 恒流源电路

电阻R2起到对运放的保护浸染,这个值不能太大,一样平常取值10R旁边。(一点小履历吧,我们设计的产品中一样平常都有加)……

原文链接:https://www.dianyuan.com/eestar/article-5372.html

三极管事理特性先容,教室上可不这么讲!

本日先容下三极管的特性,清晰易懂,老师可不这么讲。

我们平时所说的三极管全称是双极性晶体管(bipolar junction transistor),具有两个PN结,PNP型三极管电路符号如下所示,常日有B:基极base;C:集电极collector;E:发射极emitter三个引脚,怎么判断晶体管是NPN还是PNP呢?符号中的箭头都是从P指向N的,下面左图中,箭头从中间的P指向N,所有是NPN;而右图中,是从P指向中间的N,所有是PNP。

本日以NPN三极管为例,先容下三极管的特性。下面的曲线是NPN三极管的输出特性曲线,横坐标是CE之间的电压VCE,纵坐标是CE之间的电流ICE。三极管有三个事情区,分别是饱和区、放大区和截至区。

饱和区的特点是,三级管的电流与IB和VCE有关,但是与VCE干系程度更大,由于可以看到当VCE固定时,不同的IB变革引起的IC变革不大;但是反过来,IB固定,VCE变革一点点就会引起IC剧烈变革,换句话说三极管已经饱和了,已经不受控于IB而受控于VCE了。饱和的意思便是满了,我们可以用向水杯子倒水的模型来理解这个过程,IB便是倒水的水流,IC便是水面的高度,VCE便是指水杯的高度。饱和便是指水满了,如下图饱和时状态所示,此时水面高度IC已经满了(已经饱和)不受控于IB了,而受控于水杯的高度VCE,如果想要进一步增加IC,就须要增加水杯高度VCE,这样理解饱和这个观点就更形象易懂了。放大区的特点是,随着IB的增加,IC也增加,IC紧张受控于IB,与VCE关系不大,上图清晰地描述了这个征象。普通点说便是用IB来掌握IC,所有三极管是电流掌握型器件。还是以水杯模型来加深影象,下图中放大状态的水杯中,不管水杯高度VCE是多高,IC的高度只受控于IB。截至区的特点是,不管VCE怎么变革,只要IB即是0或靠近于0,IC也就约即是0,我们还是以水杯为模型来加深理解,下图中注入杯中的水龙头IB水流非常小,靠近于0,所有不管水杯VCE多高,水杯中的水IC始终靠近于0……

原文链接:https://www.dianyuan.com/eestar/article-5034.html

三极管线性稳压电路事理与仿真

刚入电源行业的时候,看同行前辈画的电路图,例如反激电源构造中,赞助绕组给芯片供电的电路中(尤其是宽电压输出的电路)基本上都会加一个线性稳压电路,如下图。当时不理解是什么事理,现在我打算用Pspice仿真来剖析这个电路。如果剖析有什么不对的地方,敬请示正。

在以上线路中,经由二极管D5整流之后,可以视EC5两端的电压为纹波很小的直流。在输出负载在较大范围内变革时,由于变压器的耦合浸染,赞助绕组两端的感应电压会有较大变革,此时一样平常须要利用线性稳压电路,在Q3发射极输出一个相对稳定的电压值,来担保芯片供电电压不会过高触发过压保护。

上图中Q3,ZD2,R26组成了一个线性稳压网络。事情事理:我们把EC5上电压视为Vin,把EC6上电压视为Vout,情形1:Vout↓ - Vbe↑ - Vce↓ ,导致Vout=Vin-Vce会上升,情形2:Vout↑ - Vbe↓ - Vce↑, 导致Vout=Vin-Vce会低落,由此可见,全体调节过程为负反馈调节,终极达到一个动态平衡,即Vout=Vb-Vbe,这里Vbe=0.7V,Vb即为ZD2的稳压值。

搭建仿真事理图:

仿真结果(第一次利用稳压管仿真折腾了良久,末了创造模型中BV值取的是管子稳压值下限):

模型中稳压管的稳压值有点偏差,因此这里在三极管基极加直流源再仿一次……

原文链接:https://www.dianyuan.com/eestar/article-4947.html

两个三极管组成的DC24V转12V电路案例剖析

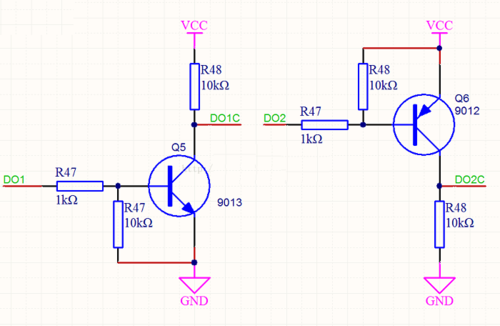

电路如下图所示,大致剖析:

图1 电路图

两个NPN三极管搭建的直流降压稳压电源(至于为什么能够稳压,可以参照我前面发的文章《这两个三极管是怎么做到恒流的?一起来剖析一下》 )输入电压DC24V,经由三极管Q1本身承受一定的压降后,输出电压Vo。

这里要重点强调一下Q1和Q2的事情状态,它们都只能事情在放大状态,为什么呢?

这个电路的目的是降压,以是Q1不可能事情在饱和状态,否则Vo=Vin=24V,就起不到想要的效果。Q2也不可能事情在饱和状态,否则输出电压Vo始终被钳位在5.6V-0.7=4.9V。

电阻R3的浸染是给稳压管D1供应一定的电流,让三极管Q2的基极电压一贯处于5.6V的稳压状态。

电阻R2的浸染是为三极管的基极供应一定的偏置电压。

小伙伴们提出如下问题:

问题1:为啥我算出来10.5V不对?

问题2:输出电压是多少?怎么算的?

问题3:把R2调大,输出电压为什么减小了呢?

咱们来逐一解答:

问题1:为啥我算出来10.5V不对?

答:10.5V是怎么来的呢?很多朋友可能是这样算的:通过稳压管为5.6V电压,可以求出三极管Q2的基极电压为5.6V+0.7V=6.3V。

R4的电流可算出:IR4=6.3V/R4=6.3V/15K=0.42mA,

输出电压Vo=IR4(R1+R4)=0.42mA25K=10.5V。

看起来彷佛没啥问题,但忽略了一点,把三极管Q2的基极电流给忽略了。

精确该当是:IR1=Ib(Q2)+IR4

以是,电阻R1和R4通过的电流实际上是不一样的。这种算法是不对的,以是10.5V的结果也是不对的。

图2 三极管Q2的基极电流

问题2:输出电压是多少?怎么算的?

答:为了便于描述,我将各岔路支路进行了标号,如下图所示:

图3 为方便打算,将各岔路支路编号

打算如下:

对付三极管Q2:

三极管Q2基极电压被钳位,以是其基极电压为5.6V+0.7V=6.3V,

I6=6.3V/R4=6.3V/15K......①

I5=(Vo-6.3V)/R1=(Vo-6.3V)/10K......②

I7=I5-I6......③

联立①②③得

I7=(Vo-6.3V)/10K-0.42mA......④

对付三极管Q1:

忽略三极管基极的电流(本身流过的电流较小)

利用Ic=βIb得:

I8=βI7,假设放大倍数β=100

则:

I8=100I7......⑤

由于Q1的基极电压被钳位,以是其基极电压为Vo+0.7V,

I8=24-(Vo+0.7V)/R2=24-(Vo+0.7V)/1K......⑥

联立①②③得I7=24-(Vo+0.7V)/(1001K)......⑦

根据④和⑦相等,可以求出:

Vo=11.66V……

原文链接:https://www.dianyuan.com/eestar/article-4686.html

三极管设计电源的开关电路

在《三极管设计逻辑取反电路(一)》的文档中,基于三极管的特性,将逻辑取反电路的参数进行了详细的打算,并给出了电阻取值的情由,但选型中没有对非常主要的一个器件——三极管进行剖析。下面一起看看对付“逻辑取反”电路和常见的开关电源里面的“开关电路”利用的三极管在选型方面有哪些须要把稳的地方。

01. 逻辑取反电路

在逻辑取反电路中,掌握旗子暗记幅值为5V,低压小旗子暗记,如果此时电源VCC电压的幅值较大,是高压旗子暗记。此时的电阻R5为阻性负载,Uce的波形如下:

当开关S0闭合时,三级管Q3饱和导通,根据电路理论:Uce+Ur=VCC,由于此时Q3的导通,压降险些为0,则此时Uce=0;

当开关S0断开时,三级管Q3截止,根据电路理论:Uce+Ur=VCC,由于此时Q3未导通,电路中没有电流,则Ur=0V,此时的Uce=VCC。

因此Uce的波形如上图2波形所示。在幅值上Uce比5V大,在相位上和掌握旗子暗记相反。电路既能实现逻辑取反,也能实现电平转换,同时还是小旗子暗记掌握大旗子暗记理念的表示。

在《三极管设计逻辑取反电路(一)》中针对三级管开通和关断的韶光,进行了电阻的调度,但是未对三极管集电极承受的电压进行打算。从Uce的波形上可以看出,如果三极管要能正常的开通和关断,在集电极承受的电压最小为0V,最大为VCC。

考虑到安全裕量,开关管的耐压值Uce=(1.2~1.5)xVCC

举例:根据2N3904数据手册,三极管的VCE最大为40V。如果将该型号的三极管用在电路中,VCC的电压不能超过40/1.5=28V,即在VCC电压为30V以下的电路都是比较安全的。

02. 开关电源的开关电路

在逻辑取反电路中,集电极和VCC之间接的R5为阻性负载,如果将阻性负载改为感性负载——电感(变压器)。这种电路在隔离式开关电源的拓扑中会常常看到,如下图的反激式拓扑所示。

为了方便剖析,将隔离式开关电源的中的开关电路部分进行单独剖析,如下图5所示。

如果测试2N3904的Uce之间的波形,在示波器上常常会看到下面的波形,即在方波上还有一个振荡的波形……

原文链接:https://www.dianyuan.com/eestar/article-1253.html

更多精彩内容,尽在电子星球 APP(https://www.eestar.com/)

宝藏半导体技能文章合集,送你!

来囤超超超多的技能仿真实例啦!

PWM搞不定,读完此文得心应手

快速入门PWM的技能难点,从此开始!

这样理解PWM就对了!