CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体)技能出身于飞兆(仙童)半导体公司研发实验室。1963年,C.T.Sah和Frank Wanlass提交了一篇关于CMOS工艺制程技能的论文,首次在半导体业界提出CMOS工艺制程技能。

1974年,美国无线电公司推出RCA1802为标志,业界首次将CMOS工艺制程技能用于制造微处理器芯片。迄今为止,其在业界的运用已有四十多年的历史。这里将对其发展史做一个大略的科普性的概括先容。

双极型工艺是最早运用于实际生产的集成电路工艺制程技能。1951年贝尔实验室制造出世界上第一个锗双极型晶体管,1956年德州仪器(TI)制造出第一个硅双极型晶体管;1970年,硅平面半导体工艺制程技能发展成熟,双极型晶体管(bipolar junction transistor, BJT)开始大批量生产。

双极型晶体管的实物图、电路事理图、工艺剖面图

双极型工艺具有制造流程大略、制造本钱低、良率高档优点。其余,在制备的电路性能方面,其具有高速率、高跨导、低噪声、和强电流驱动能力等上风,常日用于电流放大型电路、功率放大型电路和高速电路等。它是电流掌握型的电路器件,一贯在高速电路、仿照电路、功率电路等中占主导地位。缺陷是集成度低、功耗大,在超大规模集成电路中的运用受到很大限定。20世纪70年代,CMOS工艺集成电路开始在逻辑运算领域逐步取代BJT的统治地位。但在许多仿照器件和大功率器件领域,BJT依然霸占主要地位。

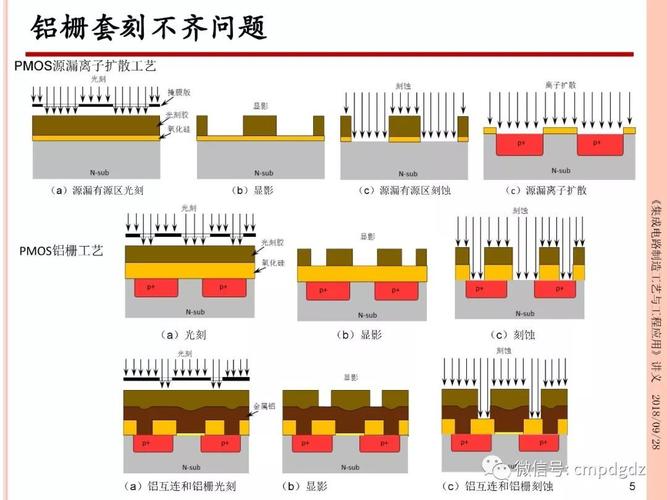

PMOS工艺PMOS(P-Channel Metal Oxide Semiconductor, P型沟道金属氧化物半导体)工艺涌如今20世纪60年代,是最早涌现的MOS工艺技能。PMOS器件是制备在n型衬底上的p沟道器件,最早是利用铝栅掌握器形成反型层沟道,沟道连通源极和漏极,使器件开启而导通。PMOS是电压掌握型器件,依赖空穴作为载流子进行导电事情。空穴的迁移率较低,以是PMOS器件的速率很慢,最小的逻辑门延时也有100纳秒。但它的功耗较低,比较适用于逻辑运算集成电路,加之其速率较慢的劣势,其工艺技能紧张运用于腕表以及打算器等对打算速率哀求较低的领域。

PMOS时钟集成电路实物图、PMOS示意图、PMOS工艺剖面图

NMOS工艺NMOS(N-Channel Metal Oxide Semiconductor, N型沟道金属氧化物半导体)最早涌如今20世纪70年代初期。与PMOS器件相同,NMOS器件也是电压掌握型器件,但由于其事情的导电载流子是电子,比空穴具有更高的迁移率(大约是空穴的2.5倍),因而其电流驱动能力是PMOS的2倍多,因而用NMOS工艺技能制造的集成电路性能比PMOS工艺更高。符合业界向高性能集成电路发展的哀求,因而,NMOS一经推广便很快取代了PMOS制程技能。与BJT技能比较,NMOS技能又具有高集成度,制备本钱更低等上风,NMOS技能逐渐在逻辑门电路方面超越BJT技能。此时的集成电路集成度可达上万个门器件。但正是由于集成度的增加,单个门器件功耗一定的情形下,当器件的集成度从1000门到达10000门时,高集成度的芯片功率从几百毫瓦达到几瓦,只能利用昂贵的陶瓷封装代替便宜的塑料封装,大大增加了生产本钱,限定了NMOS工艺技能在更高集成度的进一步运用。

NOMS逻辑电路图、NMOS示意图、NMOS工艺剖面图

CMOS工艺1963年,C.T.Sah和Frank Wanlass提交了一篇关于CMOS工艺制程技能的论文,首次在半导体业界提出CMOS工艺制程技能,为CMOS技能的发展奠定了理论根本。CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体)是把NMOS和PMOS同时制造在一个衬底上组成集成电路。其利用互补对称电路来对PMOS和NMOS进行互连形成路基电路,其静态功耗险些靠近为零。很好的办理了NMOS的功耗问题。

CMOS反相器电路

1966年,美国无线电公司研制出首颗CMOS工艺门阵列(50门)集成电路芯片。但当时技能限定下,其集成度并不高,速率也比较慢,而且随意马虎引起闩锁效应烧毁电路,因而早期的CMOS工艺技能受到半导体业界的冷落。

20世纪70年代LOCOS隔离技能的发明、离子注入技能对离子扩散技能的取代,前辈光刻技能的不断发展,大大改进了CMOS工艺制程技能。此时的技能节点已进入亚微米阶段。

20世纪90年代,STI、Salicide(金属硅化物)等技能手段运用于CMOS工艺技能,CMOS工艺制程不断更新,特色尺寸不断缩小,CMOS工艺集成电路事情速率不断提高,高集成度、强抗滋扰性、高速率、低功耗、宽的电压掌握范围使其逐渐成为集成电路芯片制备的主流技能。

基于LOCOS技能的CMOS工艺剖面图、基于STI和金属硅化物的CMOS工艺剖面图

进入21世纪,CMOS工艺制程技能飞速发展,应变硅技能、HKMG(High-k Metal Gate, 高k金属栅技能)的涌现使得平面CMOS的特色尺寸缩减至深亚微米(几十纳米)。这一期间CMOS技能的发展深刻印证了摩尔定律的准确性。

摩尔定律与平面CMOS工艺技能节点发展

平面CMOS到三维CMOS当集成电路芯片制造家当的特色尺寸缩小到22nm时,利用传统的CMOS平面微纳加工工艺技能,已经不能完备办理由于其沟道尺寸的缩小而带来的器件性能劣化的问题。在平面器件中,随着特色尺寸的进一步减小,对付极薄的栅极氧化层,虽然可以通过栅极电压对沟道进行掌握,但这将导致泄电流的增加,终极导致载流子迁移率(μ)降落,体平面技能无法使CMOS晶体管的性能做出显著的改进。1999年,胡正明教授及其团队提出了Fin-FET (鳍式场效应晶体管),基于Fin-FET构造的CMOS晶体管,2011年Intel公司在其22nm工艺技能节点上首次推出其商品化的Fin-FET产品Ivy-Bridge。这一晶体管构造的利用大大增加了晶体管的栅控能力,也使得基于此晶体牵制备的芯片功耗显著降落。也正是Fin-FET的引入,tsmc(台湾积体电路制造株式会社,简称台积电)崛起,在14nm之后的Fin-FET技能节点发展下(14nm、7nm、5nm),Intel的霸主地位被撼动,tsmc自此成为晶圆代工技能的引领者。

平面晶体管到三维晶体管(Fin-FET构造)

目前集成电路芯片工艺发展到5nm节点,Fin-FET晶体管构造彷佛也将要到达其物理极限。上个月在日本举行的“三星晶圆代工论坛”会议上,Samsung公布了其新一代芯片制造工艺的进展。Samsung表示,只管在7nm和5nm的工艺节点上,其工艺进度都掉队于tsmc,但其表示在明年就将完成3nm工艺的研发。在3nm的工艺节点上,Sumsung通过引入Si纳米线构造,将从目前主流的FinFET晶体管构造转向最新的GAA(Gate-All-Around)环抱栅极晶体管构造,其将第一代GAA晶体管称之为3GAE工艺。可以说三星能否打一场翻身仗的关键就在于这一世代工艺能否赶超台积电。而据网络宣布,台积电3nm也已经提前启动,在男科30公顷的用地渴望年底完成交地,摆明了便是冲着着三星而开展的计策操持。台积电和三星的这场前辈工艺代工争夺战在所难免,让我们拭目以待吧。

平面晶体管到Fin-FET到GAA FET

参考文献[1] 集成电路制造工艺与工程运用。温德通 著

[2] 纳米集成电路制造工艺(第2版)。张汝京 著

[3] IEDM、VLSI 论文集

微电子学生党一枚,以上内容仅代表个人不雅观点,欢迎大家在评论区谈论呀。^_^