以碳化硅(SiC)、氮化镓(GaN)为代表的第三代半导体材料,由于其宽带隙、高电子饱和漂移速率、高热导率、大击穿场强等上风,是制备高功率密度、高频率、低损耗电子器件的空想材料。个中, SiC功率器件具有能量密度高、丢失小、体积小的上风,在新能源汽车、光伏、轨道交通、大数据等领域具有广阔的运用前景;GaN射频器件具有高频、高功率、较宽频带、低功耗、小尺寸的上风,在 5G 通讯、物联网、军用雷达等领域有广泛的运用。而在加工制备中,衬底上制备高质量外延材料是提高器件性能及可靠性,推动第三代半导体在生产生活中运用的关键,本篇姑息此做详细先容。

一、外延的基本观点

(一)定义

外延(epitaxy)成长是指在经由切、磨、抛等仔细加工的单晶衬底(基片)上成长一层有一定哀求的、与衬底晶向相同的单晶层,犹如原来的晶体向外延伸了一段。新单晶可以与衬底为同一材料,也可以是不同材料(同质外延或者是异质外延)。由于新生单晶层按衬底晶相延伸成长,从而被称之为外延层(厚度常日为几微米),而长了外延层的衬底称为外延片(外延片=外延层+衬底),器件制作在外延层上为正外延,若器件制作在衬底上则称为反外延,此时外延层只起支撑浸染。目前碳化硅和氮化镓这两种芯片,如果想最大程度利用其材料本身的特性,较为空想的方案便是在碳化硅单晶衬底上成长外延层。

外延片作为半导体原材料,位于半导体家当链上游,是半导系统编制造家当的支撑性行业。外延片制造商在衬底材料上通过CVD(Chemical Vapor Deposition,化学气相沉积)设备、MBE(Molecular Beam Epitaxy,分子束外延)设备等进行晶体外延成长、制成外延片。外延片再通过光刻、薄膜沉积、刻蚀等制造环节制成晶圆。晶圆再被进一步切割成为裸芯片,裸芯片经因为基板固定、加装保护外壳、导线连接芯片电路管脚与外部基板等封装环节,以及电路测试、性能测试等测试环节终极制成芯片。

(二)外延的意义

外延成长技能发展于50年代末60年代初,当时为了制造高比年夜功率器件,须要减小集电极串联电阻,又哀求材料能耐高压和大电流,因此须要在低阻值衬底上成长一层薄的高阻外延层。外延成长的新单晶层可在导电类型、电阻率等方面与衬底不同,还可以成长不同厚度和不同哀求的多层单晶,从而大大提高器件设计的灵巧性和器件的性能。外延技能浸染紧张表示在:

1.可以在低(高)阻衬底上外延成长高(低)阻外延层。

2.可以在P(N)型衬底上外延成长N(P)型外延层,直接形成PN结,不存在用扩散法在单晶基片上制作PN结时的补偿的问题。

3.与掩膜技能结合,在指定的区域进行选择外延成长,为集成电路和构造分外的器件的制作创造了条件。

4.可以在外延成长过程中根据须要改变掺杂的种类及浓度,浓度的变革可以是陡变的,也可以是缓变的。

5.可以成长异质、多层、多组分解合物且组分可变的超薄层。

6.可在低于材料熔点温度下进行外延成长,成长速率可控,可以实现原子级尺寸厚度的外延成长。

7.可以成长不能拉制单晶材料,如GaN,三、四元系化合物的单晶层等。

(三)外延的紧张制备工艺

对付化合物半导体来说,外延伸短常主要而又分歧凡响的工艺,而对付不同的材料和运用,紧张有分子束外延(MBE)、金属有机化学气相沉积(MOCVD)、氢化物气相外延(HVPE)、液相外延(LPE)等。比较之下,MOCVD技能成长速率更快,更适宜家当化大规模生产;而MBE技能优点是材料的质量非常好,但是成长的速率比较慢,在部分情形如PHEMT(高电子迁移率晶体管)构造、Sb锑化合物半导体的生产中更适宜采取;HVPE(氢化物气相外延)技能在氮化镓和氮化铝材料外延上运用较多,目前大部分HVPE设备是自行搭建的,很少有商业化的设备,优点便是成长速率比较快;LPE(液相沉积)是比较早期的外延方法,紧张用于硅晶圆,目前已基本被气相沉积技能所取代。

MBE 与 MOCVD 技能比拟

二、GaN的外延

不同于Si和SiC芯片,GaN的外延片常日用的是异质衬底,例如蓝宝石、碳化硅、硅等是氮化镓外延片主流的异质衬底材料。从理论上来讲,GaN同质衬底是成长GaN外延层最好的衬底,这样就不存在品质失落配和热失落配问题,成长出来的外延膜质量将大大提高,位错密度也可降到很低,同时发光效率、器件事情电流密度均会提高。但由于GaN在常压下无法熔化,高温下分解为Ga和N2,在其熔点(2300℃)时的分解压高达6GPa,当前的成长装备很难在GaN熔点时承受如此高的压力,因此传统熔体法无法用于GaN单晶的成长。

各种衬底材料比较

(一)GaN on SiC的制备

宽带隙的碳化硅与GaN晶格失落配较小、导电、热导率高,在目前半导体照明芯片上霸占上风,将在一定韶光范围内领先其他技能方案。SiC衬底的缺陷是价格昂贵、折射率较大、毛病密度高、热失落配也较大,由于SiC表面随意马虎形成一种稳定的氧化物,阻挡其分解和刻蚀,因此SiC衬底在外延成长前的表面处理非常主要。目前主流SiC衬底尺寸是4-6英寸,8英寸衬底仅有少数公司节制制造技能,半导电型SiC衬底以n型衬底为主,紧张用于外延GaN基LED等光电子器件、SiC基电力电子器件等,半绝缘型SiC衬底紧张用于外延制造GaN高功率射频器件。在金属有机化学气相沉积的过程中,包含了繁芜的持续串过程:

首先,先驱物借由高精准度的注入喷头(Injector)精确地掌握进入汽化反应(Vaporizer)及制程反应腔体(Reactor)反应物的量,并且借由反应气体与其进行化学反应。这些反应后的金属有机化合物,会在基板的表面进行吸附(Adsorption)、表面反应(Surface kinetics)、薄膜发展(Growth),形成一层薄膜。末了,这些未参与反应的反应物,则会进行脱附(Desorption)、真空排气(Evacuation)等过程,使制程反应腔体能保持真空且纯净的环境。采取SiC为衬底的GaN外延成长方法示例:

1.MOCVD成长依次将氮化钛层、氮化铝层和氮化镓层沉积在SiC衬底上,气氛因此三甲基镓(TMGa)、三甲基铝(TMAl)、三甲基钛(TDEAT)和氨气(NH3)分别作为Ga、Al、Ti和N源,以氢气(H2)为载气。首先,将SiC衬底置于1200度反应室进行前烘300s,降温至500度,通入氨气8000sccm对衬底进行氮化;

2.然后通入TDEAT三甲基钛气体,流量掌握在40sccm,并连续通入氨气8000sccm,时长80s,进行氮化钛沉积,250s进行复原;

3.然后通入TMAl三甲基铝气体50sccm,10000sccm氨气,时长100s,进行氮化铝沉积;

4.末了通入TMGa三甲基镓气体。80sccm,15000sccm氨气,时长150s,进行氮化镓沉积,对反应室气氛复原,完成缓冲层成长。

各家GaN外延成长方法knowhow不一样,属于机密配方。

(二)技能难点

GaN on SiC是目前氮化镓外延的主流技能,紧张技能难点如下:

1.衬底表面氧化层、亚表面损伤层、毛病等影响 GaN 外延层的质量;

2.GaN 在SiC 衬底表面难以成核,由于 Ga 原子在 SiC 衬底表面浸润性差,直接在 SiC 衬底表面成长 GaN 成长速率慢、材料质量差;

3.衬底表面原子排布勾引 GaN 外延层中形成堆垛层错(BSFs),对付 SiC 衬底上外延 GaN,衬底上有多种可能的原子排列次序,导致其上外延 GaN 层初始原子堆垛次序分歧一,随意马虎产生堆垛层错。堆垛层错(SFs)沿着 c 轴引入内建电场,导致面内载流子分离以及器件泄电等问题涌现;

4.晶格失落配与热失落配问题。SiC 衬底与 GaN 晶格常数与热膨胀系数不同,使 GaN 层受到压应力,热膨胀系数差异导致成长完成后的降温过程中 GaN 薄膜受到张应力。应力与 GaN 带隙呈线性关系,每 1Gpa 双轴应力带来的带边峰的线性移动为 20±3meV。此外,应力的存在导致 GaN 外延层中产生了高密度的毛病。

(三)办理方案

1.SiC 衬底表面处理

SiC 衬底表面处理是 SiC 衬底外延 GaN 面临的主要问题之一。早期由于 SiC 衬底切磨抛工艺过程带来的划痕、亚损伤层、污染物残留等问题较多,随着 SiC 晶圆切磨抛工艺以及衬底封装工艺的进步, 衬底表面质量得到改进。目前 SiC 衬底表面采纳机器化学抛光的处理办法已做到基本无划痕, 氮气氛围的封装工艺也可避免 SiC 表面与氧气的永劫光打仗, 因此多数外延不再采取额外的化学堕落,而是直接采取原位高温 H2 或 H2/NH3稠浊气体高温热处理的办法进行衬底处理。

2.外延成长调控

直接在 SiC 衬底表面外延成长 GaN,由于两者间原子浸润性差,GaN 在衬底表面为 3D 岛状成长,外延层受到的应力全部开释,只保留了降温过程中产生的张应力。引入 AlN 缓冲层可有效改进原子浸润性,使 GaN 外延层呈二维成长,缓冲压应力的开释, GaN 外延层仍旧保持压应力状态,从而提升 GaN 外延层结晶质量。

(a)GaN/SiC (b)GaN/AIN/SiC外延成长模式

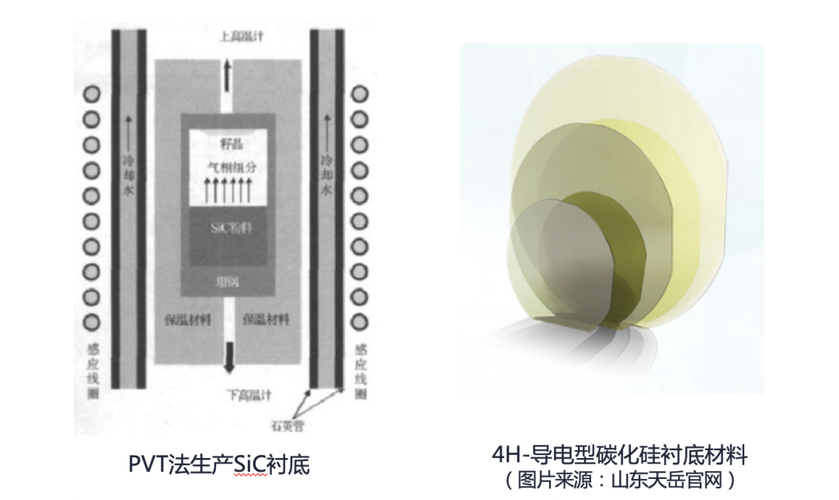

三、SiC 的外延

(一)SiC on SiC的制备

为制作功率器件,须要在碳化硅衬底上成长1层或几层碳化硅薄膜,目前主流的方法是采取CVD法进行同质外延成长,其优点在于对外延层厚度及杂质掺杂的精确掌握和均匀性,但有严重的多型体稠浊问题。早期碳化硅是在无偏角衬底上外延成长的,然而受多型体稠浊影响,实际外延效果并不理想,难以进而制备器件。之后发展了利用台阶流成长方法在不同偏角下斜切碳化硅衬底,使外延表面形成高密度的纳米级外延台阶,可在1500℃旁边的温度下制备均一相的外延层。

台阶掌握外延法的优点在于不仅能够实现低温成长,而且能够稳定晶型的掌握,其成长温度可以降至1200℃乃至更低而不产生3C-SiC夹杂相,但随着温度降落,表面毛病密度和背景氮掺杂浓度会显著增加,成长速率也会受到较大影响,因此选择得当的温度和衬底偏角是实现SiC外延快速高质量制备的关键。另这种方法的毛病在于无法阻断基平面位错和对衬底材料造成摧残浪费蹂躏。经由几十年的不断发展完善,台阶掌握外延法己经比较成熟,成为了碳化硅外延的紧张技能方案。

为了打破台阶掌握外延法的限定,TCS(三氯氢硅)法应运而生,可以同时实现成长速率大幅提升和质量的有效掌握,非常有利于SiC厚膜外延成长。TCS技能率先由LPE在2014年实现商业化,2017年旁边Aixtron对设备进行了升级改造,并将该技能移植到了商业的设备中。

(二)主要指标和参数

1.高质量厚膜外延

SiC功率器件中,在外延的 SiC 漂移层中平衡外延层厚度及掺杂浓度是得到高耐压器件的关键。一样平常低压在600伏,须要的外延厚度大概在6个μm旁边,中压1200~1700,厚度便是10~15个μm。高压1万伏以上,大概须要100个μm以上。以是随着电压能力的增加,外延厚度随之增加,高质量外延片的制备也就非常难。

SiC 双极器件中击穿电压对漂移区掺杂浓度和厚度哀求

2.掺杂浓度掌握

掌握外延层的掺杂浓度对 SiC 功率器件的性能至关主要。外延层掺杂浓度与掺杂源流量、C/Si 比、温度、反应室压强、成长速率等成长参数有关。除掺杂浓度以外,外延层的掺杂均匀性是研究者们的另一关注重点,下图(a)展示了衬底转速对径向 n 型掺杂浓度均匀性的影响。可以看出,从衬底中央到边缘,掺杂浓度逐渐增加。提高衬底转速可有效提升载流子浓度分布的均匀性;(b)展示了成长速率对径向掺杂浓度均匀性影响,随着成长速率的升高,径向掺杂浓度均匀性降落。合理的掌握外延成长速率有利于掺杂浓度与均匀性的调控,然而 SiC 厚膜外延须要高的成长速率,因而在外延成长过程中,须要基于外延目的调控外延成长参数,终极得到符合哀求的外延材料。

(a)衬底转速;(b)成长速率45(三角形)、54(空心圆)、77(实心圆)um/h对径向掺杂浓度均匀性的影响

3.毛病调控

有效调控 SiC 外延层中的毛病是确保 SiC 功率器件性能与可靠性的关键。SiC 外延层中的毛病紧张分为层错、位错、表面毛病及点毛病。致命性毛病像三角形毛病、滴落物,对所有器件类型都有影响,包括二极管、MOSFET、双极性器件,影响最大的便是击穿电压,它可以使击穿电压减少20%,乃至跌到90%; 非致命性毛病如一些TSD和TED,对二极管可能没有影响,但对MOS、双极器件有寿命的影响,或者泄电的影响,终极影响器件的加工合格率。以是在碳化硅外延中毛病的掌握非常关键。

SiC中的(a)三角形毛病(b)胡萝卜毛病(c)彗星型毛病

四、紧张外延厂家

(一)GaN外延厂家

GaN外延片干系企业紧张有比利时的EpiGaN、英国的IQE、日本的NTT-AT。中国厂商有苏州晶湛、苏州能华、英诺赛科、聚能晶源和世纪金光等企业,个中苏州晶湛2014年就已研发出8英寸硅基外延片,现阶段已能批量生产;苏州能华2017年建成8英寸氮化镓芯片生产线并正式启用;英诺赛科的8英寸硅基氮化镓生产线2017年投产,成为海内首条实现量产的8英寸硅基氮化镓生产线;聚能晶源2018年12月成功研制了 8 英寸硅基氮化镓(GaN-on-Si)外延晶圆;世纪金光官网显示已实现以氮化镓基外延片为主的生产和发卖。

(二)SiC外延

环球纯粹做碳化硅外延,范例的便是中国的大陆的EpiWorld(瀚每天成)、东莞天域以及台湾的嘉晶电子。业内的龙头是Cree旗下的Wolfspeed(IDM模式),除了对外供应衬底片和外延片,还做器件、模块。同时日本昭和电工也是优胜的碳化硅外延供应商。目前,海内瀚每天成、东莞天域半导体均可供应4-6英寸外延片,中电科13所、55所亦均有内部供应的外延片生产部门。