J-Flash SPI 许可通过 J-Link 或 Flasher 烧录器直接编程 SPI Flash。 Flash利用 SPI 协议通过 J-Link 直接编程,中间没有 CPU / MCU。

通过 J-Link 直接编程 SPI 闪存(中间没有 CPU / MCU)由于 J-Link 直接与闪存通信,因此纵然连接到 J-Link 不支持的 CPU 的闪存也可以编程跨平台(GUI 和命令行版本适用于 Windows、Linux 和 macOS)自动检测盛行的 SPI 闪存可以支持任何 SPI 闪存。 如果须要,可以手动配置/覆盖所有闪存参数可以通过命令行掌握目录

License容许20 pin 连接20 pin QSPI 连接10 pin 连接支持哪些 SPI flash?命令行版本J-Link硬件版本具有哪些软件和硬件功能?J-Flash SPI - 大略有效的SPI Flash编程工具

J-Flash SPI 许可通过 J-Link 或 Flasher 直接编程 SPI flash, flash利用 SPI 协议通过 J-Link 直接编程,中间没有 CPU / MCU。

大多数常见的 SPI flash都可以通过其各自的 ID 自动识别,并且可以轻松编程,无需用户对 J-Flash SPI 进行进一步的设置/配置。

J-Flash SPI 直接烧录SPI Flash芯片界面

License容许为了利用 J-Flash SPI,可以利用更高真个 J-Link型号(J-Link PLUS 或更高版本)的烧录器或 Flasher in-circuit programmers。

J-Link烧录器型号及支持的烧录软件

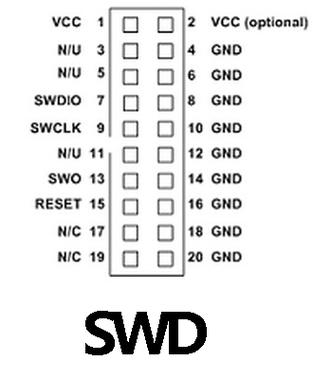

20-pin 连接下表列出了 J-Link / Flasher 上 SPI 接口的引脚排列。

Pinout SPI 20-pin

Pin

Signal

Type

Description

1

VTref

Input

This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor.

2

Not connected

NC

Leave open on target side.

3

Not connected

NC

Leave open on target side.

5

DI

Output

Data-input of target SPI. Output of J-Link, used to transmit data to the target SPI.

7

nCS

Output

Chip-select of target SPI (active LOW).

9

CLK

Output

SPI clock signal.

11

Not connected

NC

Leave open on target side.

13

DO

Input

Data-out of target SPI. Input of J-Link, used to receive data from the target SPI.

15

nRESET

Output

Target CPU reset signal (active LOW). Typically connected to the reset pin of the target CPU, which is typically called "nRST", "nRESET" or "RESET".

17

Not connected

NC

Leave open on target side.

19

5V-Supply

Output

This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin.

引脚 4、6、8、10、12 是 J-Link 中连接到 GND 的 GND 引脚。 它们还应连接到目标系统中的 GND。

注:SPI接口所利用的接口与JTAG是复用的

管脚序号

JTAG定义

SPI定义

5

TDI

MOSI

7

TMS

nCS

9

TCK

SCK

13

TDO

MISO

20 PIN QSPI 连接下表列出了 quad SPI (QSPI) 接口的引脚排列。

Pinout QSPI 20-pin

Pin

Signal

Type

Description

1

VTref

Input

This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor.

2

Not connected

NC

Leave open on target side.

3

IO1

I/O

Bi-directional data I/O pin 1

5

IO0/DI

I/O

Single: Data-input of target SPI. Output of programmer, used to transmit data to the target SPI.Quad: Bi-directional data I/O pin 0

7

nCS

Output

Chip-select of target SPI (active LOW).

9

CLK

Output

SPI clock signal.

11

IO2

I/O

Bi-directional data I/O pin 2

13

DO

Input

Single: Data-out of target SPI. Input of programmer, used to receive data from the target SPI.Quad: Must be connected to same signal as pin 3 IO1/DO to guarantee correct operation for temporary single mode transfers during QSPI mode.

15

nRESET

Output

Target CPU reset signal (active LOW). Typically connected to the reset pin of the target CPU, which is typically called "nRST", "nRESET" or "RESET".

17

IO3

I/O

Bi-directional data I/O pin 3

19

5V-Supply

Output

This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin.

引脚 4、6、8、10、12 是 J-Link 中连接到 GND 的 GND 引脚。 它们还应连接到目标系统中的 GND。

10-Pin 连接如下图所示为J-Link烧录器通用转接板。

J-Link烧录器通用转接板

该转接板各接口点位定义如下图所示。

转接板接口点位定义

下表列出了利用J-Link烧录器通用转接板时 J-Link/Flasher 上 SPI 接口的引脚排列。

Pin

Signal

Type

Description

1

VTref

Input

This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor.

4

nRESET

Output

Target CPU reset signal. Typically connected to the RESET pin of the target CPU, which is typically called "nRST", "nRESET" or "RESET".

5

DI

Output

Data-input of target SPI. Output of J-Link, used to transmit data to the target SPI.

6

DO

Input

Data-out of target SPI. Input of J-Link, used to receive data from the target SPI.

7

nCS

Output

Chip-select of target SPI (active LOW).

9

CLK

Output

SPI clock signal.

10

GND

Input

Reference GND.

引脚 3 是连接到 J-Link 中的 GND 的 GND 引脚。 它也该当连接到目标系统中的GND。

关于nRESET的把稳事变:如果有另一个器件/外设也掌握SPI flash(例如flash连接的CPU),J-Link的nRESET该当连接到目标系统的复位或CPU的复位引脚,确保在对 SPI flash进行编程时,J-Link 可以保持 CPU 处于复位状态。

J-Flash SPI connection

支持哪些 SPI flash?J-Flash SPI 能够通过芯片ID 自动检测常见的 SPI Flash。此外,由于Flash参数(大小、指令等)也可以由用户手动配置,因此可以支持任何 SPI Flash型号。 可在官网找到 J-Flash SPI 支持的Flash芯片列表,地址为:

https://www.segger.com/products/debug-probes/j-link/technology/cpus-and-devices/supported-spi-flashes/

J-Flash SPI 不支持 Atmel DataFlash,由于它的指令集和一样平常处理与任何其他 SPI 闪存明显不同

命令行版本J-Flash SPI 的命令行版本也可用于 Windows、Linux 和 macOS,命令行版本也是 J-Link 软件和文档包的一部分。 请把稳,也可以从命令行掌握 J-Flash SPI 的 GUI 版本。

命令行版本

JFlashSPI_CL.exe是JFlashSPI的命令行工具,通过输入命令实现读写Flash。

-connect连接,-open打开烧写文件,-auto烧写,如果是烧写,这3个命令就够了,首先把要烧写的文件复制到JFlashSPI_CL.exe同级目录,输入指令:

JFlashSPI_CL.exe -open UNIGBK.BIN 0 -connect -auto

可以将以上命令写成一个批处理命令,直接双击运行即可。新建.bat文件,并以记事本办法打开,输入以下内容:

JFlashSPI_CL.exe -open UNIGBK.BIN 0 -connect -autoecho 程序烧写完成!

pause

然后将这个bat文件和要烧写的字库文件放到一个文件夹下。双击直接运行就可以直接烧写,是不是方便了许多呢?

J-Link硬件版本具有哪些软件和硬件功能?硬件版本为V9及以上的才支持J-Flash SPI软件。

J-Link BASEJ-Link BASE

J-Link PLUSJ-Link PLUS

烧录IS25LP064A芯片示例IS25LP064A为ISSI旗下的NOR Flash,64Mbit 。该芯片引脚定义如下:

IS25LP064A引脚定义

烧录时,烧录器与该芯片的连接关系如下表所示:

烧录器管脚序号

JTAG定义

SPI定义

芯片管脚序号

芯片管脚定义

1

VTref

VTref

8

Vcc

4

GND

GND

4

GND

5

TDI

MOSI

5

SI(IO0)

7

TMS

nCS

1

CE#

9

TCK

SCK

6

SCK

13

TDO

MISO

2

SO(IO1)

此外,烧录时该芯片的WP#(IO2)、HOLD#(IO3)管脚须要上拉至3.3V。