针对上述研究现状和分布式采集场景剖析,本文先容了一种基于FPGA和TOE架构,实现TCP/IP协议数据传输的多路采集与切换系统。该系统涉及并行、多路通道切换、TCP/IP协议通信等模块,并通过上位机PC(或键盘与LCD)进行远程(或本地)准确掌握与实时显示,知足多路通道切换、仿照旗子暗记并行采集、可靠性传输等功能的需求。

1 系统总体设计

该系统包含上、下位机设计,组成一个完全的多路采集与切换系统,系统总体设计框图如图1所示。上位机部分中的PC掌握与显示子系统,可根据监测需求,远程对下位机进行配置和支配,并实时显示获取的数据。LCD显示与键盘掌握子系统,与下位机安装为一体,可独立地对下位机进行通道掌握与旗子暗记检测,提升该系统的便捷性和实用性。下位机作为该系统的主体部分,紧张由基于FPGA芯片的核心调度、数据处理、通道管理、旗子暗记调理与采集、网络通信、串口通信、单片机掌握及电源与时钟管理七大模块组成。FPGA核心调度模块是下位机的核心部分,完成对下位机各个模块间的折衷运行与逻辑掌握,实现全局时钟管理、TCP/IP协议与串口通信、命令和数据的组帧与解析、通道切换与配置、旗子暗记采集与数据处理等功能。

基本事情事理:系统上电后,首先等待FPGA初始化,完成默认配置,被测外围接口保持关闭,下位机处于TCP做事器模式,等待上位机连接。上位机PC连接成功后,进行通道切换与选择命令配置,并通过以太网将命令数据传至下位机。然后,下位机通过以太网通信模块吸收TCP数据,解析数据获取命令后,逐一对各通道管理模块进行配置,切换到被测通道,并对个中8路通道的电压和电流进行旗子暗记调理与采集。每次采集的数据和状态信息,再通过数据处理模块组帧后,交付给以太网通信模块以TCP/IP协议发送数据至上位机。末了,上位机对吸收数据进行剖析和显示,完成对多路通道的远程切换、采集与监测。

若无PC连接,系统可利用键盘进行命令配置,LCD显示部分测试结果,采取串口通信与下位机进行命令和数据的交互,实现本地便捷掌握与监测。

2 系统硬件及FPGA设计

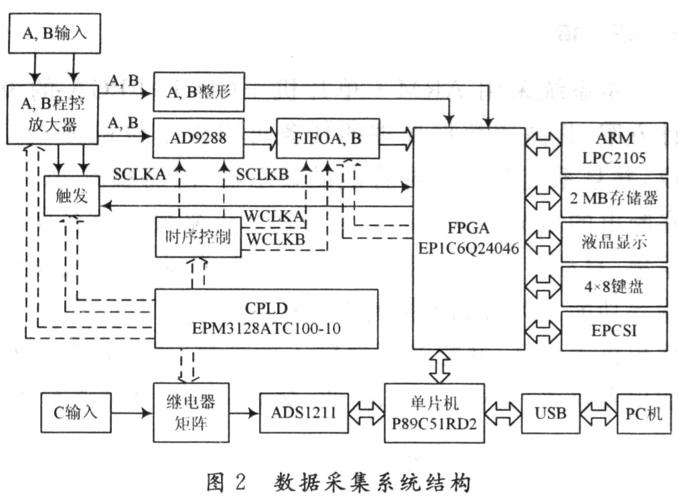

多路采集与切换系统的硬件设计紧张由电源与时钟模块、FPGA逻辑掌握模块、以太网通信模块、通道管理与切换模块、ADC旗子暗记采集模块和STM32掌握模块组成,硬件设计构造框图如图2所示。

2.1 FPGA逻辑掌握模块

FPGA逻辑掌握模块采取了基于Xilinx公司Spartan-6系列的XC6SLX150-2FG484C开拓的核心板AC6150具有高速、高带宽、高容量等特点。这款核心板尺寸为60 mm×60 mm,搭载FPGA上电配置功能,扩展用户I/O接口168个,并具备丰富的内部逻辑资源。其作为载板直插利用,为工程技能职员供应了一个简便的FPGA利用方案,极大降落了设计繁芜度与周期。

FPGA是下位机部分的核心掌握单元,逻辑设计采取硬件描述措辞(Verilog HDL)和集成开拓套件ISE14.7实现。FPGA逻辑掌握模块的顶层设计包括时钟管理与系统复位、W5500掌握、数据处理、通道切换、AD采集掌握以及STM32掌握等子模块,顶层模块卖力各个子模块的连接和逻辑综合,FPGA顶层设计构造如图2中间虚线框中所示。

2.2 以太网TCP/IP通信模块

以太网TCP/IP通信模块紧张采取WIZnet公司的一款多功能全硬件以太网接口芯片W5500,内部集成10/100 M以太网掌握器,嵌入TOE技能,支持TCP、UDP、IPv4等协议,无需考虑协议内部各层关系,不涉及操作系统,只须要精确配置就可以实现网络连接,接口电路大略、编程灵巧方便[8-9]。该模块电路如图3所示。

FPGA基于SPI(外部串行接口)协议对W5500内部的寄存器区和内存进行读写访问。寄存器区由通用寄存器区(用于配置网关、子网掩码、源IP和源MAC地址等)和8个Socket_n(0≤n≤7)寄存器区(用于配置Socket端口号、模式、配置命令等)组成。W5500内嵌32 KB缓存(吸收内存和发送内存,各占16 KB),用于缓存以太网传输中已吸收和待发送的用户数据。

采取FPGA+W5500的办法实现基于TCP/IP协议的硬件通信系统设计,具有状态稳定、体积小、本钱低、高速可靠等上风。FPGA通过W5500掌握子模块实现W5500的状态机掌握和SPI协议通信,实现对W5500芯片的掌握和数据交互。W5500的状态机掌握包括对W5500掌握器的状态初始化、寄存器配置、TCP连接管理、内存数据读写等功能,其主掌握状态机状态转移如图4所示。

FPGA逻辑设计中,将W5500配置为TCP做事器模式,等待上位机PC(作为客户端)进行主动连接。建立连接后,PC下发通道切换、采集等命令数据,通过以太网传输至W5500。FPGA检测到W5500吸收中断后,从W5500吸收缓存中读取数据,然后交给数据处理模块,进行数据解析,并将命令信息下发到干系掌握模块。

数据处理模块紧张完成对吸收(和待发送)的TCP数据进行解析(和组帧);W5500掌握模块的核心在于TCP的连接建立、数据吸收和数据发送掌握。利用Socket_0作为与上位机通信的端口,TCP通信建立、数据收发流程如图5所示。经回环测试,TCP传输最高速率达40 Mb/s,知足浩瀚嵌入式运用需求。

2.3 通道管理与切换模块

通道管理与切换模块采取通道选通芯片(ADG1408YRUZ)、电平转换芯片(LSF0108DCUR)、掌握切换芯片(ADG819BRM)和继电器(G3FD-X03SN)组成,以实现对外围不同接口管脚的选通、驱动和掌握。通道选通芯片实现8通道选一的选通功能;掌握切换芯片和继电器掌握外围输入通道是否接入;FPGA管脚输出电平为3.3 V,难以直接驱动外围器件,通过电平转换芯片将输出转换为5 V,以提高驱动能力。

当数据解析模块收到通道切换命令后,FPGA通过通道切换子模块,实现对外围芯片的掌握,完成多路不同通道的管理和切换。

2.4 ADC旗子暗记采集模块

ADC旗子暗记采集模块由电压采集和旗子暗记调理子模块组成。电压采集子模块选用ADI公司的高精度模数转换芯片AD7609BSTZ,它是一款18位、8通道、真差分、同步采样模数数据采集系统(DAS) ,最高吞吐率达200 kS/s。该系统采取2片AD7609芯片分别对8路被测通道的电压和电流进行采集,仿照旗子暗记输入范围采取±5 V。在采集前端,连接旗子暗记调理子模块,选用电流转电压芯片(MAX4080SASA+)将被测电流旗子暗记转换为仿照电压旗子暗记,再经由电压旗子暗记调理芯片(AD8276ARZ)和适当高精度电阻进行分压,使输入AD芯片的被测仿照旗子暗记范围在-5 V~+5 V之间。

FPGA完成对通道的管理切换后,通过AD采集掌握子模块,开启对接入被测的8路通道AD采集。采样频率为10 kHz,16路并行采集,采样速率达2.88 Mb/s(16×18 bit×10 kHz/s)。AD采集掌握子模块采取串行事情办法,每完成一次采集,将数据交由数据处理子模块进行组帧,再通过W5500将数据以TCP/IP协议传输至上位机PC。

3 系统软硬件综合测试

3.1 FPGA逻辑设计仿真与测试

进行FPGA逻辑设计时,仿真剖析是必不可少的环节,利用ISE14.7自带的仿真软件ISim和在线逻辑剖析软件ChipScope,有利于验证设计的精确性,提高设计效率。由于篇幅有限,以下针对该系统FPGA设计的重难点模块之一——以太网TCP/IP通信模块的W5500数据发送功能,进行仿真和测试剖析。

以太网TCP/IP通信通过掌握W5500实现,对W5500掌握模块进行数据发送测试仿真如图6所示。在吸收到命名标志Cmd_Receive后,将测试数据Test_Data_r[7:0]依次存入B_FIFO中,再以单bit的办法从B_FIFO中读出,结合SPI协议将数据发送至W5500发送缓存;数据全部写入后,给出写入完成标志W5500WrFlag,以此开启W5500进行TCP数据发送。利用ChipScope对实测旗子暗记在线“抓取”,得到W5500数据发送测试旗子暗记截图如图7所示,实测与仿真结果同等,表明该设计的精确性。

3.2 系统测试与效果

下位机采取标准2U机箱设计,可同时连接8台被测设备,每台设备有13路不同的接口,共需掌握8组×13路通道的切换。上位机的命令配置界面如图8所示,通过勾选通道组合,实现多通道选择和切换命令的配置。图8中展示了同时开启对8台被测设备的2通道监测,并施加掌握旗子暗记1、4的命令配置过程。

利用网络封包剖析软件WireShark对系统的TCP/IP传输过程进行测试,下位机为做事器(IP:192.168.1.168,端口号:10000),上位机PC为客户端(IP:192.168.1.1,端口号:8001),TCP/IP通信测试的流量统计结果如图9所示。图中给出“三次握手”建立TCP连接,和命令数据发送吸收与ACK回答过程,表明TCP/IP通信正常。

在2号通道接入被测器件,上位机采取图8中的通道切换命令配置,系统测试对应的PC和LCD监测显示结果如图10所示,PC在报表界面可实时显示被测8路通道的电压和电流,LCD以10 Hz的频率刷新显示监测结果。阅历久试验和测试结果表明,PC与LCD显示结果与实际同等,测试效果良好,显示画面稳定,操作便捷流畅。

4 结论

本文设计了一种基于FPGA和TCP/IP协议的多路采集与切换系统,其采取FPGA+W5500的办法实现了基于硬件的TCP/IP协议栈,并详细先容了该系统的TCP/IP通信、通道切换和多路采集部分的设计方法。综合测试结果表明,系统可以实现多路采集与切换掌握的功能,稳定可靠、利用便捷,具有一定的实用代价。

参考文献

[1] BAO S,YAN H,CHI Q,et al.A FPGA-based reconfigurable data acquisition system for industrial sensors[J].IEEE Transactions on Industrial Informatics,2017,13(4):1503-1512.

[2] 李洋,禹卫东,胡骁,等.基于FPGA的千兆以太网数传系统设计[J].电子丈量技能,2015(10):72-77.

[3] 周浩,王浩全,任时磊.基于FPGA和NAND Flash的便携式旗子暗记采集系统设计[J].电子技能运用,2018,44(9):88-92.

[4] ZSEBY T,IGLESIAS V F,BERNHARDT V,et al.A network steganography lab on detecting TCP/IP covert channels[J].IEEE Transactions on Education,2016:1-9.

[5] LIU Q,XU Z,LI Z .Implementation of hardware TCP/IP stack for DAQ systems with flexible data channel[J].Electronics Letters,2017,53(8):530-532.

[6] 谢喆.基于FPGA的TCP/IP数据通信的设计与运用[D].武汉:武汉科技大学.

[7] 高柯柯.基于FPGA和W5500的串口数据切换系统研究与设计[D].兰州:兰州交通大学,2017.

[8] 王文,郑建生.基于FPGA的TCP/IP网络通信系统的设计与实现[J].当代电子技能,2018(8):5-9.

[9] 彭海,高俊雄,王耘波.基于FPGA的虹膜图像采集系统设计[J].仪表技能与传感器,2016(1):43-46.

作者信息:

王 威1,张秋云1,江 虹1,余恒松2,易志强1,朱 笛1

(1.西南科技大学 信息工程学院,四川 绵阳621010;2.西南科技大学 国防科技学院,四川 绵阳621010)