ARM自动驾驶打算平台配置

图片来源:互联网

ARM针对汽车功能安全的Split/Lock/Hybrid模式

图片来源:互联网

在汽车功能安全标准ISO26262-5 2018产品开拓:硬件层面附录D对处理单元的诊断覆盖率推举的安全技能方法中,作为可实现高诊断覆盖率的几种技能方法之一,硬件冗余技能中,双核锁步、非对称冗余、编码打算是三种范例的技能方法。

锁步是两个核运行同样的程序,将结果输入一个比较逻辑中,周期性比较两个核的输出结果是否相同,即CCM。如果相同,则连续运行;否则,则需采纳一定的方法。若一段韶光后缺点还是存在,可能重启或者重新检讨。锁步核的设计是固定在芯片设计中的,以是没有可调度性。随意马虎看出,锁步核虽用了两个核,但实在只起到一个核的浸染,摧残浪费蹂躏了一个核。这种方法已在微掌握器和繁芜度较低的微处理器领域经由多年的成功验证。如果是设计比较繁芜的核,纵然未有非常,两个核之间也可能不同步。目前再进一步是将比拟结果输出到一个被称为“safety island”安全岛的核中,由这个核卖力决策和实行。这个核利用单独的时钟和电源,且有很高的安全性能。这种方案提升了系统繁芜度,但软件实行更加灵巧。ARM一样平常推举是Cortex-R52。

ARM有双重锁步能力,第一重在CPU内部,利用DSU实现,第二重在CPU外部,利用安全岛实现。DSU是DynamIQ Shared Unit ,第一次涌现是在A75上。

ARMDSU运用示例

图片来源:互联网

DSU基本构成

图片来源:互联网

DSU的核心功能是掌握CPU内核,使其成簇Cluster利用,簇内每一个核心可以单独开关、调度频率/电压,能效表现更佳,乃至制造商是可以将不同核心(目前仅支持Cortex-A75与Cortex-A55)以不对等的数量放到一个簇内,可以Cortex-A75×3+ Cortex-A55×5,也可以Cortex-A75×1+ Cortex-A55×7,兼顾本钱与性能。再有便是L3缓存的共享。DSU能够利用CCI、CCN或是CMN不同总线技能,把CPU与SoC里其它单元(GPU、Modem、内存)高速连接起来;如果它拥有4MB三级缓存,能以动态办法分配缓存给每个核心,比如说Cortex-A75×1+ Cortex-A55×7下,可以将3MB缓存分配给A75核心,剩下7个A55核心共享1MB缓存,乃至可将三级缓存交给GPU等单元利用,灵巧性非常高;最主要的是它还卖力掌握簇内每个CPU核心开关、频率高低、电压大小,是掌握CPU性能与功耗的关键。

在设计DynamIQ之时ARM还考虑到冗余需求,比如比较智好手机,汽车对可靠性、冗余度哀求赶过不少,DynamIQ许可多个簇通过CCIX连接在一起,这样处理器就可以分布于汽车不同位置,当发生交通意外一个簇受损时,DynamIQ技能可以调用出备用途理器,担保汽车正常运转。

Cortex-A78AE的DSUAE内部框架图

图片来源:互联网

DSU AE紧张是添加了比较器,再有便是亮色部分都复制一份,包括实行逻辑、时钟、功率状态,各个界面,当然缓存不能复制,那样本钱太高,也意义不大。

DSU-AE锁步模式

图片来源:互联网

DSU-AE分离模式

图片来源:互联网

DSU-AE稠浊模式

图片来源:互联网

DSU-AE界面

图片来源:互联网

除了DSU还有针对汽车功能安全的GPU架构G78AE,图像ISP的C71AE,中断掌握GIC-600AE,存储管理MMU-600AE,网格总线CMN-600AE。但DSU最关键。

二、ARM的片上总线

ARM智能驾驶产品全系列

图片来源:互联网

数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛运用。在基于IP复用的SoC设计中,片上总线是连接各模块,对各模块做出仲裁的核心系统,是设计最关键的问题。AMBA总线是ARM研发的(Advanced Microcontroller Bus Architecture)供应的一种分外的机制,可将RISC处理器集成在其他IP芯核和外设中,是有效连接IP核的“数字胶”,并且是ARM复用策略的主要组件。它不是芯片与外设之间的接口,而是ARM内核与芯片上其他元件进行通信的接口。AMBA规范紧张包括了AHB (Advanced High PerformanceBus)系统总线和APB (Advanced Peripheral Bus)外围总线。除了AMBA总线,ARM还有应对多核的GIC中断掌握,MMC内存掌握。

ARM CMN-700

图片来源:互联网

ARM发展了一种介于总线和NoC之间的连接系统,称之为CMN,紧张用于连接CPU内核,也可以CPU内核和加速器之间的连接。采取MESH网格构造,但没有路由功能,实质上还是总线,但MESH网格支持的单元很多,远比一样平常总线要多,最高可支持512核,支持512MB的L3缓存,目标市场紧张是HPC领域。

CMN-700同时还支持AMBA AXI5、ACE5-lite、CXS和CCIX

附录:ARM架构一览

干系阅读深入理解汽车系统级芯片SoC连载之六:CPU微架构

深入理解汽车系统级芯片SoC连载之五:指令集与运算架构

深入理解汽车系统级芯片SoC连载之四:缓存、超标量、乱序实行

深入理解汽车系统级芯片SoC连载之三:ARM的商业模式与CPU微架构概览

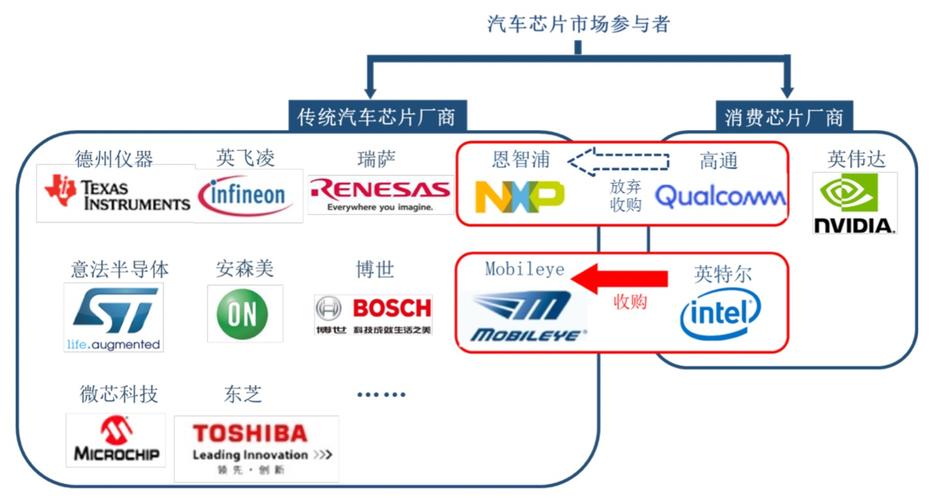

深入理解汽车系统级芯片SoC连载之二:汽车芯片家当及供应链

深入理解汽车系统级芯片SoC连载之一:汽车系统级芯片概览及AEC-Q100车规

报告订购及互助咨询请私信

佐思 2022年研究报告撰写操持

智能网联汽车家当链全景图(2022年2月版)

更多佐思报告

主机厂自动驾驶

汽车视觉(上)

高精度舆图

商用车自动驾驶

汽车视觉(下)

高精度定位

低速自动驾驶

汽车仿真(上)

OEM信息安全

ADAS与自动驾驶Tier1

汽车仿真(下)

汽车网关

汽车与域掌握器

毫米波雷达

APA与AVP

域掌握器排名剖析

车用激光雷达

驾驶员监测

激光和毫米波雷达排名

车用超声波雷达

红外夜视

E/E架构

Radar拆解

车载语音

汽车分时租赁

充电根本举动步伐

人机交互

共享出行及自动驾驶

汽车电机掌握器

L4自动驾驶

EV热管理系统

稠浊动力报告

L2自动驾驶

汽车功率电子

汽车PCB研究

燃料电池

无线通讯模组

汽车IGBT

汽车OS研究

汽车5G

汽车线束

线控底盘

合伙品牌车联网

V2X和车路协同

转向系统

自主品牌车联网

路侧智能感知

模块化报告

自主品牌ADAS研究

商用车车联网

商用车ADAS

汽车多模态交互

汽车智能座舱

车载显示

Tier1智能座舱(上)

座舱多屏与联屏

智能后视镜

Tier1智能座舱(下)

智能座舱设计

汽车照明

座舱SOC

汽车VCU研究

汽车座椅

汽车数字钥匙

TSP厂商及产品

HUD行业研究

汽车云做事研究

OTA研究

汽车MCU研究

AUTOSAR研究

聪慧停车研究

传感器芯片

软件定义汽车

Waymo智能网联络构

ADAS/AD主控芯片

T-Box市场研究

自动驾驶法规

ADAS数据年报

T-Box排名剖析

智能网联和自动驾驶基地

汽车镁合金压铸

乘用车摄像头季报

智能汽车个性化

翱翔汽车

专用车自动驾驶

农机自动驾驶

矿山自动驾驶

港口自动驾驶

自动驾驶重卡

无人接驳车

仪表和中控显示

车载DMS

合伙品牌ADAS

环视市场研究(本土篇)

800V高压平台

商用车ADAS

环视市场研究(合伙篇)

汽车无线模组

EDR行业研究

「佐思研究月报」

ADAS/智能汽车月报 | 汽车座舱电子月报 | 汽车视觉和汽车雷达月报 | 电池、电机、电控月报 | 车载信息系统月报 | 乘用车ACC数据月报 | 前视数据月报 | HUD月报 | AEB月报 | APA数据月报 | LKS数据月报 | 前雷达数据月报