确实,MOS管作为电容,比较利用金属电容来讲,同样容值哀求下,可以节省不少面积。

这是为什么?MOS电容有哪些上风和缺陷?

这是本篇文章想要回答的内容。

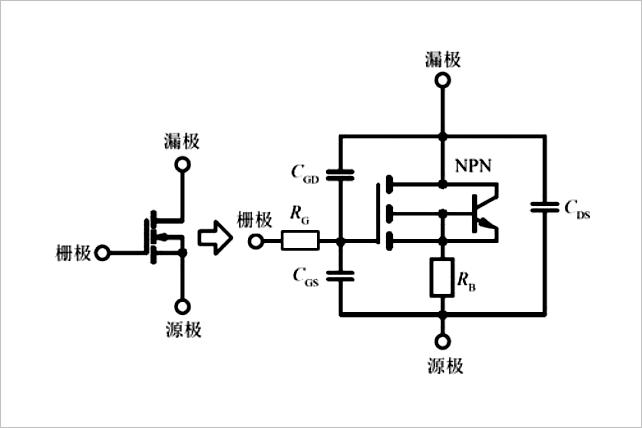

MOS管电容的事理

MOS管形成电容的紧张事理,便是利用gate与沟道之间的栅氧作为绝缘介质,gate作为上极板,源漏和衬底三端短接一起组成下极板。

以下图的NMOS管为例。

Figure 1. NMOS的剖面图

它的源漏和沉底连到一起到地,gate上有一个电压源。

当gate的电源大到一定程度,超过阈值电压VTH,会引起源漏之间涌现反型层,即沟道形成,这样栅氧就充当了gate与沟道之间的绝缘介质,一个电容就形成了。这个电容的单位面历年夜小,与栅氧的厚度和介电常数有关。

如果gate电压是个比地还低的电压,这个时候源漏之间的N型沟道不能形成,但是却会使P型衬底的空穴在栅氧下方累积。如此一来,gate与衬底之间仍旧会形成电容,此时的绝缘介质仍是栅氧,以是此时与形成沟道时的电容大小几无二致。

如果gate电压处在一个不尴不尬的位置,既不能使源漏之间形成沟道,也不能使P型衬底的空穴在上方积累。此时可以认为,栅氧下方会形成一个空间电荷区,这个空间电荷区是电子与空穴结合后形成的区域,以是它不带电,是一个“绝缘体”。由此,你该当清楚了,这个“绝缘体”会与栅氧这个绝缘体相叠加,导致等效的绝缘介质厚度增加,以是电容值随之低落。

下方的曲线可以解释上面先容的情形。

Figure 2. 电容与栅压的变革曲线

为什么会省面积

上面的先容,我们知道,当沟道或者积累区形成,栅氧是MOS电容真正的绝缘介质。栅氧的厚度和介电常数对电容的大小起决定性浸染。

常日来说,除非是低介电常数(low-k)工艺,一样平常的工艺,金属电容之间的绝缘介质的介电常数和栅氧的介电常数,相差无几。

以一个工艺资料来看,一个是3.9,一个是4.2。差别较小。

而如果比较两种绝缘介质的厚度,那就会差很多。一样平常来讲,栅氧厚度会偏小(尤其是低压MOS),比金属电容之间的绝缘介质的厚度可以小很多。

同样拿我手头的工艺资料来参考,5V MOS栅氧厚度13nm,1.8V MOS栅氧厚度4nm,而金属电容,单位面积1fF的绝缘层厚度为64nm,单位面积1.7fF的绝缘层厚度会小一些,但是也要37nm。以是就厚度来讲,后者比前者最少也要大3倍旁边。

这便是MOS管做电容会节省面积的缘故原由。

MOS电容上风与缺陷

实在上面的一节,就已经说出了MOS电容的上风在哪里了。

MOS电容紧张的上风便是节省面积、方便,由于它本身便是MOS管,与身边电路中的其他MOS管同为兄弟姐妹,想用的话,随手就可以扔进电路。

缺陷也是很显而易见,便是MOS电容实在是个“压控电容”,当高下两个极板的压差发生变革,容值也会随着改变,这在哀求高精度的电路中,险些是致命的。微弱旗子暗记采集的前端仿照电路中,它压根不敢露面。

但是在一些哀求不是很严格的电路中,例如给数字旗子暗记的延时模块等,MOS电容可以充当电容的完美替人。随手便是一个电容,隐蔽在许多MOS管的军队中,神不知鬼不觉。

其余一个不随意马虎想到的缺陷是,MOS电容的耐压特性很差。这是由于它的绝缘介质利用了栅氧,栅氧较薄。5V MOS电容,能承受的电压在5V附近,1.8V MOS电容,能承受的电压在1.8V附近。而金属电容,有的却可以承受几十伏的高压。这也是电路设计中,为什么只管即便避免电源与地之间利用MOS电容去耦的缘故原由所在。

INSIGHT

总结一下,MOS电容的优点:

1,单位容值较大,可以省面积。

2,利用方便。

缺陷:

1,实在是个MOS变容器,容值会随电压而变。

2,耐压差。

你看,MOS电容,不是一个多么伟大的创造,它有上风,缺陷也不少,不过是你在电路设计中多了一个分外的选择而已。

除了知道MOS电容的优缺陷,对MOS电容形成机制的理解和理解,会让我们设计电路时更加游刃有余。

该内容是小编转载自网络,仅供学习互换利用,如有侵权,请联系删除。如果你还想理解更多关于电子元器件的干系知识及电子元器件行业实时市场信息,敬请关注微信公众年夜众号 【上海衡丽贸易有限公司】