本文设计了一种I2S音频数据处理电路,以I2S协议为根本,利用HV2芯片和FPGA开拓板,实现I2S音频数据的传输,办理跨时钟域传输数据的问题。利用CTS天生器改进电源抑制,降落输动身抖和噪声性能。仿真测试表明音频数据能够被完全的传输。

4K电视画面质量明显提升,已经成为当今电视的主流发展方向。电影电视工程师学会(SMPTE)定义了4K视频传输的SDI接口。原始的4K音频数据无法直接被SDI接口利用。本文基于SMPTE协议,利用FGPA开拓板进行数据转换和处理,再插入视频数据流中。I2S协议能够将数据旗子暗记和时钟旗子暗记分开传输,避免了时差诱发的失落真,故采取I2S协议制作音频接口。

I2S(inter-IC sound bus)是飞利浦公司为数字音频设备之间的音频数据传输制订的一种总线标准,既规定了硬件接口规范,也规定了数字音频数据的格式。如图1所示,对应数字音频的每一位数据,BCLK(串行时钟)都有1个脉冲。LRCLK(帧时钟)是运用于变更旁边声道数据的时钟,其频率即是采样频率。LRCLK必须与BCLK保持同步。

图1 I2S通信时序图

2 I2S接口硬件设计利用HV2芯片吸收并处理音频数据。HV2芯片是由socionext研发的影像接口转换器,紧张用于2~4K视频数据的转换,并能处理与传输I2S音频数据[6]。HV2处理后的I2S音频数据对应于不同的声道进行音频数据传输,再由FPGA的I2S模块吸收。

本文将HV2的采样时钟设定为48kHz,同时规定LRCLK的高电平表示传输的是左声道,低电平表示传输右声道,并设定传输数据的最大数据位宽为32bit。实际测试中只吸收到24bit数据。根据I2S协议,在数据传输过程中,若LRCLK的单次脉冲宽度不能将须要传输的全部bit数据完全传输,则截断低位的bit数据,而在完全的bit数据传输完成之后,LRCLK的周期还没有结束,则系统会在低位处自动补齐。故在配置输出时设置位宽32bit,可避免将尾部的bit数据截断,从而传输完全的bit数据。

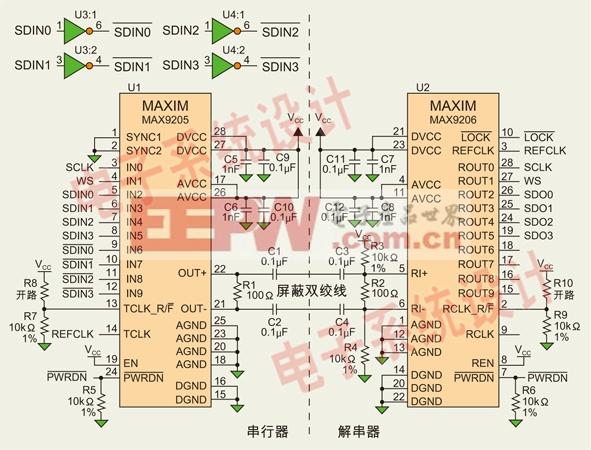

SDATA数据线上的有效数据也是24bit。时钟频率是由HV2中的晶振产生并掌握,LRCLK为48kHz,而BCLK为3.072MHz。如图2所示,4路串行数据线I2S_SD0、I2S_SD1、I2S_SD2和I2S_SD3分别对应着不同方位的声道,从而传输7.1立体声音频。

图2 I2S电路设计图

如图3所示,传输sd_i0的数据,经由i_ws旁边声道选择,并经由数据拼接和补码转换终极得到o_Left_LFE_data和o_Right_FC_data。ws_reg_i和left_code_flag是标志位,根据其状态判断当前是否须要进行数据拼接和补码转换。

图3 I2S数据的传输

3 在FPGA中传输音频数据本文所用的FPGA开拓板是代号为XC7A50T- 3FGG484的芯片(以下简称“X3芯片”),能够实现音视频的吸收、发送等功能内嵌I2S模块。X3芯片的核心逻辑功能电压是2.5V,I/O端口的电压是3.3V,知足HV2数字端口的所规定电平的哀求。

如图4所示,图中既标识了I2S接口的引脚信息,也标记了FIFO的引脚信息。FIFO_D0至FIFO_D15、FIFO_FULL和FIFO_EMPTY用于测试异步FIFO跨时钟域的空满状态,根据不同状态将进行不同的反馈。

设计中FPGA的音频吸收模块,其内部时钟是27MHz,而HV2的内部时钟为3.072MHz,导致吸收和发送处于不同的时钟域,使得这些域中的动作间没有关联性,无法完成同步,系统循环进入亚稳态[7]。为减少亚稳态的影响,应对跨时钟域问题的进行处理。异步FIFO[8]能实现大量数据的跨时钟域传输,并担保较高的数据传输速率。

如图5所示,本设计中采取双端口存储器RAM[9]来缓存系统数据,并设定其数据宽度为32bit,深度为1024bit。读、写掌握端分别掌握wrdata(写入)旗子暗记与rddata(读出)旗子暗记,利用wrfull(写满)和rdempty(读空)标志转换这两个不同时钟域的运行状态。

在异步FIFO的设计中,关键环节之一是检测并判断缓存器是否产生wrfull或者rdempty旗子暗记。不同的时钟域供应不同的时钟旗子暗记,当写掌握器吸收到写要求旗子暗记时,相应的wrcontrol(写掌握)旗子暗记随之产生,此时指针也指向将写入数据的地址。在数据写入的过程中,不断检测FIFO缓存器是否已经写满。

若未写满,则连续传输数据;否则产生wrfull旗子暗记反馈给FIFO缓存器。当读掌握器吸收到读要求旗子暗记时,相应的rdcontrol(读掌握)旗子暗记随之产生,此时指针指向将读出数据的地址。在数据不断读出的过程中,检测FIFO缓存器是否已经读空。若未读空,则连续读出数据;否则产生rdempty旗子暗记反馈给FIFO缓存器。图5 异步FIFO构造框图

格雷码具有循环特性和单步特性,当用其表示一个连续变革的数值时,仅有一个位会翻转,因此大幅度的降落位翻转的频率,从而担保传输的稳定性,减少传输误码率,故在实际操作中指针地址利用格雷码表示。正是利用了这一特点,使得能减少亚稳态的产生概率[10]。

为解释如何得到写满和读空旗子暗记,以位宽为8bit,深度为16bit为例,如图6所示。此处要设置addr(地址旗子暗记)为5bit,当读地址指针的速率高于写地址指针时,则两个指针会在某一时候指向同一个值,意味着已经读空数据,将产生rdempty旗子暗记,此时w_addr=r_addr。

而当写地址指针循环一次并追上读地址指针时,此时w_addr[4]与r_addr[4]相反,w_addr[3:0]=r_addr[3:0],表示已写满数据,产生wrfull旗子暗记。wrfull旗子暗记有效并反馈给系统时,系统将停滞写入数据;rdempty旗子暗记有效并反馈给系统时,系统将停滞读取FIFO的数据,如此就能够担保数据的精确稳定的传输。图6 读空写满标志旗子暗记的产生

在传输音频数据时,为了能改进电源抑制,降落输动身抖和噪声性能,加入了一个CTS(cycle time stamp)天生器。在LSI(大规模集成电路)上有发射器TX Pure CTS和吸收器RX Pure CTS。通过调节TX ACR(audio clock regeneration)分组和RX ACR分组的CTS的变革来减少音频时钟抖动。

如图7所示。原始的CTS经由发生器产生新的CTS,并封包成ACRPacket。CTS与NormalCTS有明显差异,CTS的变革周期变长,减少音频时钟抖动。ACR数据包是音频时钟再生数据包,这是掌握FIFO传输之后的时钟域的标准时钟。

而输入的Fs(参考旗子暗记)用于调节锁相环内部振荡旗子暗记的频率和相位,并将旗子暗记传入FIFO中,使音频数据封包成为ASP(audio sample packet)。封包输出的ASP将与HBASP(high bitrate audio stream packet)共同组成完全的音频数据包[11]。图7 TX Pure CTS发生器的框图和旗子暗记图

4 仿真结果音频模块的仿真是调用了vivado的库并在modelsim中实现的。仿真过程中,i_sck的周期为20000ps,i_sd的周期为34000ps。而从图8中可知,对应每个i_sck的上升沿所采样的i_sd数据都能准确的获取,所得到的数据对应于sd_i数据。

解释I2S接口可以准确的接到收HV2传来的音频数据。当ws_reg_i为低电平时,left_data_reg_i从10101001010110101001010010101101到010100101 01101010010100101011010再到1010010101101010 0101001010110101,每一次数据采样之后,二进制编码均舍弃最高位bit,在最末位拼接所采样的bit,可知数据能够精确拼接。当left_code_flag为高电平时,o_Left_LFE_data为11011010100101011010110 101001011,与10100101011010100101001010110101比拟,除首位与末端,别的均是取相反数,即解释能精确得到补码。

用发送和吸收文本文件的方法验证数据是否发送精确。如图9所示,o_FR_data传输32bit左声道数据,而o_FL_data传输32bit右声道数据,两者均是携带24bit有效数据并在其后拼接8bit无效数据。data则是旁边声道串行之后形成64bit数据用于传输。而o_sd0_Left_Right是旁边声道各截断了末端的8个位数之后的拼接数据,输出o_sd0_Left_Right,便能得到完全的有效数据。图8 I2S接口吸收数据仿真图

图9 FPGA中发送数据的仿真图

结论本文为理解决I2S音频数据的传输、跨时钟域问题,同时改进电源抑制、降落输动身抖和噪声性能。选择HV2芯片、X3芯片和CTS天生器,以支撑本文所涉及的硬件设计部分。对如何利用I2S接口在两个芯片间进行音频数据的传输以及如何办理跨时钟域的数据传输给出了基本的方案和流程。

仿真验证了数据能精确稳定地传输。用于本次实验的设备也将投入市场,实用代价和参考代价都将得以表示。