在路由器和交流机中,缓冲区至关主要,可以防止网络拥塞期间的数据丢失。缓冲区到底要多大?这个问题在学术界和工业界一贯备受争议。本文磋商了高端路由器中数据包缓冲的历史和演化,以期概述当前的实践和未来的趋势。

网络芯片中的缓冲区

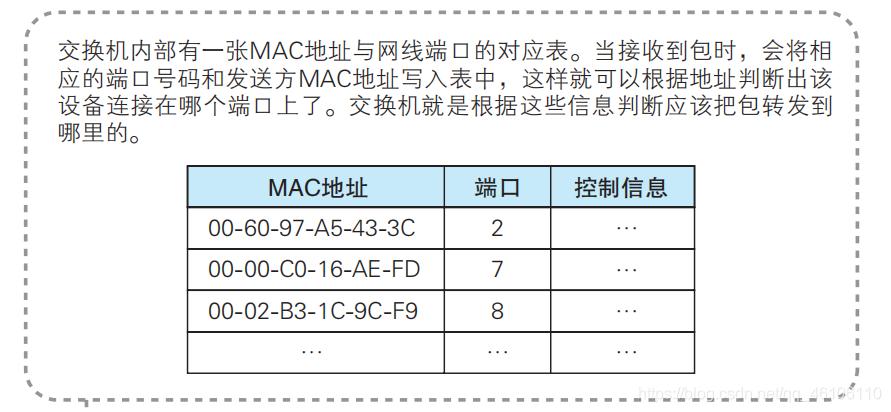

在范例的路由器/交流机 ASIC 中,会创造三种类型的数据包缓冲区。

入口缓冲区

入口缓冲区保存来自输入链路的传入数据包,而数据包头(常日是数据包的前128-256 字节)由数据包处理逻辑处理。该处理逻辑检讨数据包头中的各种协议头来打算下一跳。然后为数据包分配出口行列步队/优先级,并确定数据包必须从哪个出口输出链路转发出去。

数据包在入口缓冲区中驻留一段韶光,直到处理完成。在固定的pipeline架构中,数据包处理延迟约为 1-2 微秒。确定入口缓冲区的大小是为了在处理数据包头时保存数据包内容。

网络芯片性能的衡量标准是在不丢失数据包的情形下,每秒按线路速率可以处理多少比特的流量,以及知足该速率的最小数据包的大小。只管以太网链路上 IP 数据包最小可低至 64 字节,但许多网络芯片都会考虑到范例的网络负载,并设计数据包处理pipeline以知足远大于 64字节的数据包性能哀求,有效地减少了每秒通过芯片的数据包数量。这样做可以优化数据包处理逻辑,以节省芯片的面积和功耗。

虽然范例事情负载的均匀数据包大于 350字节,但可能会涌现小数据包的瞬时突发(常日是保持网络活动的掌握数据包或 TCP 协议的 syn/ack 数据包),这可能逾额订阅数据包处理逻辑,由于它们不是为处理如此高的每秒数据包转发而设计的。

在网络芯片中,“逾额订阅(oversubscription)”意味着资源/逻辑所承受的负载超出了其处理能力。在数据包处理逾额订阅的瞬期间间,入口缓冲区会接管数据包突发。当缓冲区已满时,它们会进行优先级感知丢弃。

延迟带宽缓冲区 (DBB)

在完成数据包处理并确定下一跳后,数据包一样平常会进入一个深度缓冲区,常日称为延迟带宽缓冲区(DBB)。当路由器的部分/全部输出链路被逾额订阅,该缓冲区将在网络瞬时拥塞期间供应缓冲。

当流经网络的流量超过网络的最大容量时,就会发生网络拥塞。造成拥堵的缘故原由有很多:

为了降落系统本钱,网络中可能会存在故意的逾额订阅。当某些用户利用的带宽超过均匀分配的带宽,就会导致拥塞;当多个主机开始相互通信时,多播/广播流量也可能导致拥塞;当端点上的某些接口涌现故障时,须要将流量分配到剩余的接口,这可能会导致上游网络设备拥塞;用户缺点,如网络配置缺点,也可能会导致拥塞;由于运用程序和用户流量的突发性,某些路由器/交流机也可能会涌现流量超过其链路容量的情形。在拥塞期间,路由器可能会创造其部分/全部输出链路被逾额订阅。在极度拥塞的情形下,所有输入流量可能都希望通过单个输出离开。在路由器芯片中设置数据包缓冲区接管瞬时拥塞,有助于整体网络的康健和吞吐量。

出口缓冲区

在网络拥塞期间,路由器须要确保高优先级流量和其他掌握流量不会涌现丢包,并且须要知足不同优先级下不同用户的做事质量(QoS)。路由器/高端交流机具有繁芜的排队和调度子系统,可以在DBB内针对不同的流掩护不同的行列步队。调度程序以不超过该接口链路容量的速率,将流量从这些缓冲区分发到输出端口接口处的浅出口缓冲区。这些出口缓冲区的大小恰好足以粉饰DBB到输出接口之间的来回时延,以便流量可以从输出接口流出,而不会涌现突发情形。

可以利用通过交流fabric互连的多个模块化路由芯片来构建大型路由器。下面将利用PFE来指代这些模块化路由芯片。

在组合输入/输出 (CIOQ) 架构中,数据包在入口 PFE 和出口 PFE上都有缓冲。如果路由器内涌现短暂拥塞,浅入口延迟带宽缓冲区会保留数据包,从而通过交流fabric将数据包从入口移动到出口。出口 PFE 处的DBB是深度缓冲区,在网络拥塞期间,数据包在个中排队较永劫光。

在虚拟输出行列步队 (VOQ) 架构中,所有延迟带宽缓冲都在入口 PFE 中完成。在这里,数据包在入口 PFE 的虚拟输出行列步队中排队。VOQ 唯一对应于数据包须要离开的终极 PFE/输出链路/输出行列步队。数据包通过出口处的繁芜调度程序从入口 PFE 移动到出口 PFE,只有在能够将数据包调度出输出链路时,该调度器才会从入口 PFE 接管数据包。在 VOQ 架构中,发往输出行列步队的数据包可在 VOQ 中的多个入口 PFE 中进行缓冲。

调度数据包缓冲区的大小两大阵营

当谈到交流机和路由器的数据包缓冲区大小时,存在着持有不同不雅观点的两大阵营:

以学者为首的阵营认为,缓冲区总体来说是臃肿的;数据中央 (DC) 网络运营商则哀求供应充足的缓冲,以避免通过其路由器/交流机的任何流涌现数据包丢失,特殊是高度分布式的云/数据挖掘运用。在大数据运用中,数百台处理查询的做事器可能会向单个做事器发送大量流量,该做事器汇总所有流的相应,这可能会导致持续数十毫秒的短暂拥塞情形。但主要的是,流量不能丢失!

DC内的存储运用对丢包也非常敏感。一样平常来说,当代数据中央的流量是双峰的,由短期、低速率的“老鼠”流和长期、高速率的“大象”流组成。大多数流是老鼠流,但它们仅承载10-15%的数据流量负载。剩余90%的流量负载由少量大象流承载。大象流对应于大数据传输,须要高吞吐量,例如备份。老鼠流对延迟敏感,由查询和掌握组成,并且须要最少的数据包丢失,以避免整体运用程序性能低落。DC 运营商更喜好更大的缓冲区,以避免老鼠流的数据包丢失,由于许多传统交流机不支持动态区分行列步队中的老鼠流和大象流。

互联网做事供应商在缓冲方面有不同的哀求,由于其路由器的重点是尽快交流大量数据,并知足视频/语音呼叫等高优先级流量的做事级别协议(SLA),他们方向于尽可能地利用昂贵/高容量的 WAN 链路,以降落设备本钱。但链路利用越频繁,丢包的可能性就越大。因此,互联网做事供应商也哀求路由器中有足够的缓冲,以区分可以容忍数据包丢失的尽力而为的流量和必须以靠近零流量丢失办法传送的高优先级流量。

在过去的二十年中,缓冲区大小一贯是个热门话题。随着路由芯片带宽的增长,内存的扩展程度却无法跟上,供应大量缓冲变得越来越昂贵。

无论是何种运用(交流/路由),全体行业的趋势都是在不影响 QoS 的情形下尽可能减少缓冲。这在很大程度上依赖流量工程、前辈的端到端拥塞掌握算法和主动行列步队管理 (AQM) 来提前向端点关照拥塞情形,并通过较小的延迟带宽缓冲区来保持链路饱和。

拥塞掌握算法

拥塞掌握算法利用的协议是闭环的,个中吸收方将收到的数据包信息发送给发送方。TCP/IP 便是这种盛行的协议套件。TCP 是一种面向连接的协议。在数据传输之前,须要在发送方和吸收方之间建立连接。TCP 从运用层的数据流吸收数据,将其划分为块,并添加 TCP报头以创建 TCP 段。然后,TCP 段被封装到 IP 数据报中,并通过网络传输到端点。

TCP 报头包含许多字段,有助于建立和掩护连接,并检测丢失的段以进行重传和拥塞掌握。个中一个字段是序列号字段。TCP 利用递增的序列号标记数据流的每个字节。当发送一个报文段时,它发送该报文段中数据第一个字节的序列号。吸收方利用序列号将无序吸收的 TCP 段组合在一起。对付吸收到的每个数据段,吸收方都会发送一个确认 ( ACK ),表示它期望从发送方收到的下一个数据段。ACK丢失则表示网络中涌现数据包丢失或网络拥塞。发送方利用此信息来降落传输速率,并重新传输丢失的段。

自 TCP/IP 出身以来,已经开拓出许多的拥塞掌握算法,帮助端点在拥塞期间调节进入网络的数据传输速率。这些算法依赖于变动拥塞窗口大小,即发送方在不等待网络拥塞确认的情形下即可发送的 TCP 段数量。

来回韶光 (RTT)

理解来回韶光对确定缓冲区大小和开拓拥塞掌握算法至关主要。RTT 是数据包从发送方传输到吸收方以及将确认返回发送方所需的来回韶光。RTT 变革很大,详细取决于端点的位置以及路径中网络设备的拥塞程度。

TCP 流的端点利用拥塞避免模式和Slow_start(慢开始)避免拥塞。

发送方一开始并不清楚网络的负荷情形,如果立即把大量数据直接注入到网络,很有可能会引起网络拥塞。以是可以由小到大逐渐增大发送的拥塞窗口值。常日一开始发送分段时,先把拥塞窗口设置为一个MSS(最大传输分段)值,收到ACK后拥塞窗口加一个分段大小,此时可以发出两个分段数据,收到两个ACK后拥塞窗口又加二,这样一轮一轮下去拥塞窗口呈指数增长,直到窗口大小达到阈值。

此时,进入拥塞避免阶段。拥塞窗口大小对每个 RTT 线性增加一个 MSS,使得每一轮不再增加一倍,而是增加一个MSS。 在此阶段,如果通过丢包检测到拥塞,则发送方将拥塞窗口减半(传输速率减半)并重新开始。

主动行列步队管理(AQM)

如果路由器等到其DBB满了后才丢弃数据包,那么在发送方对丢包做出反应之前,网络内将有更多的流量进入已经满的行列步队,导致大量的尾部丢弃(Tail-Drop)。险些所有具有深度数据包缓冲区的交流机/路由器都支持加权随机早期丢弃 (WRED),以便尽早向发送方关照拥塞情形。WRED 通过利用 WRED 曲线在行列步队满之前概任性地丢弃数据包,防止行列步队完备填满。

一些路由器和 DC 交流机还支持显式拥塞关照 (ECN)。在 ECN 中,当路由器经历拥塞时,它可能会将某些数据包标记为“经历拥塞”并按原样转发它们。IP 报头的流分类字段用于 ECN 标记。当端点收到这些设置了 ECN 位的数据包时,它们会在发送ACK的同时将拥塞情形反馈给发送方。发送方通过这些信息来降落网络传输速率。

ECN 有助于减少拥塞,且不会造成与 WRED 干系的数据包丢失,但它也有一些局限性。如果网络丢包率较高,ECN可能无法正常事情,由于标记的数据包也可能丢失,拥塞信息无法准确传达。此外,如果不同的 ECN 实现利用不同的标记算法或对拥塞的相应不同,则可能存在互操作性问题。

一些供应商集成了前辈的 AQM 技能,可以实现流量感知的早期丢弃,例如区分行列步队中的老鼠流和大象流(基于输入流量速率),并通过动态调度不同流的行列步队长度来防止老鼠流被丢弃。

缓冲区大小

确定路由器 ASIC 内部延迟带宽缓冲区大小的关键是确保当发送方因网络拥塞而停息或减少进入网络的流量时,缓冲区不会变空。当发送方因拥塞而减小窗口大小时,缓冲区充当一个储存库,以保持链路繁忙。如果缓冲区变空,则路由器的输出链路没有得到充分利用。

履历法则

过去比较盛行的规则是,一个总端口速率为C(以每秒比特为单位)的路由器,承载来回韶光为RTT的流量,就须要一个相称于RTT C的缓冲区以保持其输出链路繁忙。这称为延迟带宽积 (DBP) 或带宽延迟积 (BDP)。该规则在早期路由器中广泛利用,当时路由器的总容量小于每秒几百吉比特。

例如,在Juniper配备paradise芯片组的第一代PTX路由器中,具有 400Gbps 端口密度的 PFE 在外部存储器中供应了 4GB的数据包缓冲。这可以覆盖 80ms的 RTT ,可以知足大多数核心路由器运用。

这种根据DBP调度缓冲区大小的模型适用于两个端点之间的一些长期TCP 流,以及碰着瓶颈的单个路由器。

局限性

上述缓冲区大小的履历法则不能很好地运用到当前具有每秒TB级聚合端口带宽的路由器。例如,具有 100 毫秒 RTT 的 14.4Tbps 路由芯片将须要 144GB 的延迟带宽缓冲,这是一个非常大的缓冲区,须要放在片上或外部存储器中。

如今,HBM 存储器因其高密度和带宽被广泛用于数据包缓冲。下一代HBM3可以供应每个部件24GB的总容量。要实现 144Gb 的数据包缓冲,须要 6 个 HBM3 部件。纵然利用最大reticle-sized芯片,也很难在芯片边缘为6个 HBM3 接口腾出空间,由于大多数边缘将被高速WAN链路所需的 Serdes 占用。因此,路由器芯片必须在端口密度和供应的延迟带宽缓冲之间做出权衡。

更新的理论

路由器常日承载数千个数据流,每个流的 RTT 差异很大(这些流的端点可能不同),并且这些流很少同步。缓冲区大小的履历法则不适用于这些情形。在多流量情形下,关于缓冲区大小有着不同的研究。

斯坦福大学研究职员于 2004 年揭橥的 SIGGCOM 论文声称,对付N 个长期存在的非同步流,只需CRTT(min)/sqrt(N)的缓冲区即可保持链路繁忙。这意味着长期流越多,缓冲就越少。例如,当 10000 个长期流利过 14.4Tb路由器时,只须要 1.44GB 的延迟带宽缓冲区。这完备可以通过片上和外部存储器的组合来实现。作者还得出结论,在短期流(仍处于Slow_start阶段时结束的流)或非 TCP 流中,延迟带宽缓冲区的大小与路由器链路上的负载和流的长度成正比,并且小于C RTT_min/sqrt(N)。

随后,其他研究职员也创造,缓冲区大小取决于输出/输入容量比以及链路的饱和度。例如,如果数据中央运营商能够通过在scale-out 架构中添加更多交流机来运行未充分利用的链路,那么这些芯片中的缓冲哀求可能会低落。

只管这些论文揭橥于几十年前,但做事供应商和网络芯片供应商还没有准备好减少设备中的缓冲。直到最近几年,当内存不再随着工艺节点的进步而扩展时,他们别无选择。厂商们犹豫未定的缘故原由是很难确定N 的值,该值在韶光间隔内变革很大,详细取决于客户流量和运行在这些路由器上的运用。

学术论文常日没有考虑到现实的流量场景,大多数论文还认为短暂的数据包丢失或链路未充分利用是可接管的行为。但事实是,许多运用程序在丢包的情形下无法正常运行。这些运用须要更大的缓冲区(大约数十毫秒),以在拥塞期间缓冲对丢失敏感的流量。因此,确定缓冲区的大小是一个繁芜的决定,一个公式并不适宜所有的运用!

当代路由器和逾额订阅缓冲区

正如上文中提到的,高端路由芯片供应商面临着一个困难的选择,即在芯片/封装内的交流和缓冲能力之间进行权衡。

它们可以完备依赖片上 SRAM 进行延迟带宽缓冲。但是,片上 SRAM 的扩展跟不上工艺节点的进步。例如,在前辈的 3nm 工艺中,256MB的存储器和掌握器可以霸占reticle-sized 芯片的 15-20%。在 7.2Tbps 流量下,这相称于大约 35 微秒的 DBB。数据中央的高带宽交流机大多数流量的 RTT 小于 50 微秒。

对付支持数千个具有不同QoS属性和RTT(几十毫秒)的行列步队以及频繁发生瞬时拥塞事宜的高带宽路由芯片来说,50微秒是行不通的。这些路由芯片有两种选择:

他们可以完备依赖 HBM 等外部存储器来进行延迟带宽缓冲。但是,如果每个数据包都须要来回于 HBM,对付 14.4Tbps 的路由芯片来说,将须要足够的 HBM 接口来支持 14.4Tbps 的读写带宽。从核心芯片到 HBM 部件,很难供应如此多的 HBM 接口,同样也不可能将如此多的 HBM 部件封装在 2.5D 封装中。此外,外部存储器延迟很大,会显著增加通过路由器的排队延迟。

因此,许多高端路由 ASIC 开始利用稠浊缓冲方法,个中延迟带宽缓冲分布在片上和外部存储器之间。数据包在各自行列步队中的片上延迟带宽缓冲区中进行缓冲。排队子系统监视每个行列步队的行列步队长度。当行列步队超过可配置阈值时,到达该行列步队的新数据包将被发送到外部存储器。随着数据包从行列步队中分开,并且当行列步队不再拥塞,到达率低于出队率,行列步队长度将减少。当行列步队长度低于片上阈值时,该行列步队的新数据包将保留在片上存储器。该架构仅供应总带宽的一小部分用于外部存储器,从而减少了芯片的外部存储器接口的数量。

只管可能有成千上万个流量流经路由器,但前辈的拥塞掌握算法和更智能的网络管理可以让网络流量均匀分布,因此许多流量不会涌现持续拥塞的情形。小规模的瞬时拥塞事宜可以仅由片上缓冲器接管。只有一小部分行列步队会涌现持续拥堵。随着这些行列步队的增长,它们可以从深度缓冲区中受益。

带宽为 6.5Tbps 的下一代 24GByte HBM3 部件可为约 2.5Tbps 的输出链路供应约 70 毫秒的延迟带宽缓冲。假设在任何韶光点拥塞的流量不超过 25%,那么对付 10Tbps 路由 ASIC 来说,一个外部存储器就足够了。

构建稠浊缓冲系统

想在路由芯片中构建一个稠浊缓冲子系统,使其能够有效地利用片上和外部存储器延迟带宽缓冲并知足所有的 QoS 哀求,还存在着许多寻衅。

共享片上内存

一个空想的状态是让所有输入和输出链路完备共享延迟带宽缓冲内存的片上部分,由于可能会存在拥塞情形,即来自所有输入端口的数据包可能希望从某几个输出端口离开。在这些情形下,最好让这些行列步队占用大部分缓冲区以避免数据包丢失。

对付具有 144 个 100G 端口的 14.4Tbps 路由器来说,同时访问所有这些端口的共享延迟带宽缓冲区是一项寻衅。许多高端架构利用了两种技能让这种缓冲设计更加可行。利用宽数据总线(wide data buses)许可来自多个 100G 端口的数据包共享到共享缓冲区的同一宽接口。共享缓冲区本身被静态地划分为许多存储区,数据包被分成更小的块,并喷洒(spray)到这些存储区中,以在多个存储区上分配读/写。但这样做有一个副浸染,同一数据包的不同块从这些存储区中乱序写入和读取。缓冲区外部的掌握逻辑须要将这些事务按顺序排列,然后再呈现给下贱区块。

一些供应商进一步采取中心共享缓冲区方法,在延迟带宽缓冲区和出口缓冲区之间共享同一组片上存储器。这许可针对芯片的不同用例灵巧地划分内存。

外部内存逾额订阅管理

对付逾额订阅的外部存储器,须要繁芜的算法来决定行列步队何时移动到片外延迟带宽缓冲区。可以给每个输出行列步队分配一个配置文件,该配置文件见告行列步队在移动到外部存储器之前可以在片上添补多少。

但是,如果算法仅根据每个输出行列步队的行列步队长度做出独立决策,那么在多个输出链路极度拥塞时,它可能会决定将传入流量的很大一部分发送到片外,而外部存储器接口不一定可以处理。这给缓冲区管理逻辑增加了额外的繁芜性,须要仔细方案跨拥塞行列步队的片外移动。

跨行列步队分配片上缓冲区

在业务边缘运用程序中,在给定的韶光间隔内可能有数千个活动流。由于片上缓冲有限,不可能供应相同的行列步队阈值。这些芯片架构必须为网络运营商供应灵巧性,以便为他们配置的每个行列步队选择“配置文件”。但是,通过配置行列步队的实际流量可能与预配置速率有很大差异,这会导致缓冲区空间和资源的利用效率低下。

高等架构在基于实时行列步队耗尽率动态调度稠浊行列步队长度和片外阈值的算法上投入了大量资金,以有效地利用延迟带宽缓冲区。一些供应商还实现了高等算法来动态区分大象流和老鼠流,并通过调度这些流的缓冲区分配来防止老鼠流丢弃数据包。

数据包抖动

路由器不得对流内的数据包重新排序。但是,如果行列步队在片内和外部存储器之间移动,由于从外部存储器读取时会产生数百个周期的额外延迟,因此须要额外的逻辑来从外部存储器预取内容并保持数据包之间的顺序哀求。该预取向出口缓冲区添加了额外的缓冲区。

只管履行过程中面临着一定寻衅,但在当前工艺节点/存储器和封装技能下,稠浊缓冲可能是唯一适用于高容量路由芯片的方法。高端路由芯片供应商正不断投资高等算法,以有效利用芯片上有限的内存资源和有限的外部存储器带宽。

未来

在芯片方面,随着 3D 封装的发展,可以将多个芯片(逻辑芯片和存储芯片的稠浊)堆叠在一起。当存储器芯片层堆叠在逻辑芯片上时,逻辑芯片可从存储器得到更高的数据吞吐量,由于存储器到逻辑芯片的互连可以利用芯片的全体表面区域。目前,该技能紧张运用于针对HPC的CPU芯片。用不了多久,高端网络芯片供应商将利用这项技能来增加带宽和延迟带宽缓冲区的容量,以跟上核心内聚合的端口容量的增加。

在拥塞掌握方面,过去几十年内取得了许多进展,迄今为止已有 20 多种拥塞掌握和主动行列步队管理 (AQM) 算法。

基于延迟的算法,即发送者通过密切监视流量的来回延迟来调制进入网络的流量,变得越来越盛行。FQ-CoDel/PIE 是两种针对缓冲区膨胀的 AQM 算法。由谷歌开拓的TCP BBRv2实时构建网络模型,动态调度发送速率。与传统的基于数据包丢失的算法产生的突发比较,这些算法还可以更均匀地调配带宽,并有助于缓解大型网络中的拥塞。

学术界和工业界正在不断努力提高具有不同流量的大型网络中的拥塞掌握算法的性能、效率和公正性。基于机器学习的网络模型也正在开拓中,该模型可以学习实时拥塞情形。任何由端点持续缓解的拥塞都可以减少路由器中的缓冲区哀求。

因此,随着稠浊缓冲和主动行列步队管理技能的进步、高真个3D封装技能以及拥塞掌握算法的改进,纵然高端路由芯片的带宽每2到3年翻一番,也不须要在缓存上做出取舍。

微信搜索SDNLAB"大众号后台回答20240201,获取文中提及论文下载链接

参考

Sizing router buffers by Guido Appenzeller,作者:Guido Appenzeller、Isaac Keslassy 和 Nick McKeown - ACM SIGGCOM 2004

Updating the Theory of Buffer Sizing by Bruce Spang,作者:Bruce Spang、Serhat Arslan 和 Nick Mckeown