虽然 3D IC 技能已经是当今半导体家当炙手可热的议题,引发英特尔、台积电、三星等重兵投入,但在图像传感器 CIS 领域,3D IC 技能早已十分遍及。

武汉新芯从 2012 年投身 3D IC 技能研发 CIS 产品,至今累积了超过 84 万片晶圆出货量。

成立于 2006 年的武汉新芯,是华中地区第一个 12 寸半导体项目。

2012 年武汉新芯开始与 CIS 大厂豪威 OmniVision(已被韦尔半导体收购)互助,切入 CIS 技能与产品线。这奠定了今日武汉新芯晶圆堆叠技能的根本,公司更将 3D IC 技能作为晶圆代工业务发展的紧张平台之一。经由多年技能积累,武汉新芯已成为环球少数可供应 3D IC 代工的半导体企业之一。

2019 年 9 月,武汉新芯的母公司长江存储正式量产 64 层 3D NAND 存储芯片,其采取的 Xtacking 技能便是源于武汉新芯的 3D IC 技能,成为武汉新芯 3D IC 技能在除 CIS 之外的又一运用实例。

把两片晶圆堆叠一起,已经是现在很前瞻的技能,但武汉新芯并不知足于此。

武汉新芯晶圆代工部门业务兼行销总监沈亮表示,公司正在开拓多片晶圆堆叠技能,后续操持是实现 die to wafer 堆叠技能。

3D IC 技能已经广泛运用于 CIS 产品为什么 CIS 是目前 3D IC 技能运用最广的领域?

随着消费类产品的持续升级,大家都在同时追求更高的性能和更小的元器件尺寸。为了缩小芯片面积,遵照摩尔定律来进行晶体管微缩是常日的做法,但 CIS 芯片却无法这样做。缘故原由在于感光芯片对进光量有一定哀求,尺寸过小会影响进光量,以是须要平衡尺寸和进光量之间的关系。

以是,采取 3D IC 技能将感光芯片和逻辑电路高下堆叠起来,减小了芯片整体面积,同时担保了一定的感光面积,兼顾了性能和尺寸需求。

3D IC 运用的创新范例以长江存储 64 层 3D NAND 闪存举例。它作为环球首款基于 Xtacking 架构设计并实现量产的闪存产品,拥有同代产品中最高的存储密度。

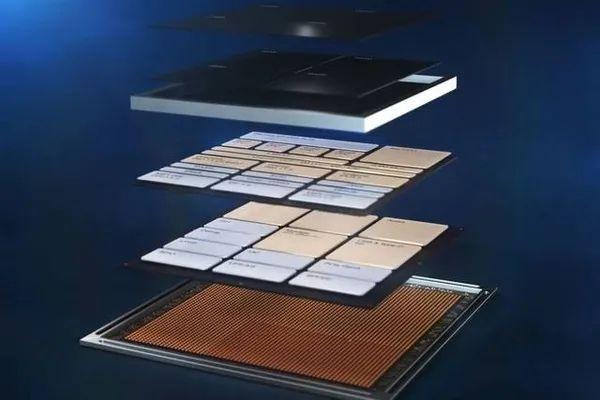

Xtacking 可实现在两片独立的晶圆上分别加工外围电路和存储单元,这样有利于选择更前辈的制造工艺。

当两片晶圆各自落成后,创新的 Xtacking 技能只需一个处理步骤就可通过数十亿根垂直互联通道(VIA)将两片晶圆键合。比较传统 3D NAND 闪存架构,Xtacking 可带来更快的 I/O 传输速率、更高的存储密度和更短的产品上市周期。

3D IC 技能最空想境界:存算一体现在人工智能是大家都非常关注的运用,办理方案有 CPU、GPU、ASIC 等,但是随着算力需求的增加,这些方案都面临“存储墙”的问题,即 CPU 和内存之间的数据传输带宽成为了瓶颈,影响了整体处理能力的提升。

最空想的办理方案,实在是在 3D 技能架构下,打造真正的存算一体,打破“存储墙”的限定。

武汉新芯已经在 2D 技能下,以 NOR Flash 架构做卷积运算,做出可事情的 AI 加速器。但是,受限于 2D 技能的周边电路构造,NOR Flash 的逻辑部分无法完成数据的快速处理。

如果采取 3D IC 技能,可以直接将一颗处理器和一颗 NOR Flash 芯片堆叠在一起,在NOR Flash中实现卷积运算和存储,在处理器和 NOR Flash 之间则可以实现数据快速传输,这样在一颗芯片中就能实现人工智能的数据运算和处理,同时,还可以用 NOR Flash 的一部分作为处理器的 embedded flash。

随着逻辑工艺进入 7nm 和 5nm,终极目的不是节省本钱,而是提升性能和缩减尺寸,但有太多无法通过工艺缩小的电路,例如仿照、I/O、嵌入式闪存等,却又霸占很大的逻辑晶圆面积,本钱高昂。

如果逻辑电路放到一片前辈工艺的晶圆上,仿照等电路移到另一片成熟工艺的晶圆上,再通过 3D IC 技能实现全带宽互联,则可以有效提高处理性能同时降落本钱。

AMD 于 2019 年初发布的新一代 CPU 便印证了这样的观点,CPU 核心用 7nm,但是 I/O 芯片是 12nm/14nm,虽然还没用到晶圆级堆叠,已然证明不同工艺的组合确实可以实现本钱可控,同时不丢失性能。

3D IC 技能的发展路径3D IC 技能可以帮忙实现创新,但也有几个痛点是无法回避的。

首先,两片堆叠的晶圆 die size 必须要做到只管即便相同,才能实现晶圆级互联时, die之间的对准。

第二个是良率掌握的问题。如果两片晶圆的良率没有掌握好,堆叠后的良率会比较低。

这也是为什么目前 3D IC 技能多用在 CIS 和存储上,由于 CIS 良率随意马虎掌握,而 NAND Flash 可以透过改动办法提升良率。

以是,对付 3D IC 项目,我们推举的互助模式是:在项目早期,武汉新芯就希望和芯片设计公司、EDA 软件厂商、终端客户来一起互助,定义产品架构、进行测试方法的开拓和验证、完成容错算法,确保产品开拓和系统开拓同步,提高产品的良率。

看好 3D IC 技能的前景和高技能壁垒,武汉新芯擘画了三个阶段的 3D IC 技能目标:

第一阶段:2020 年 Hybrid Bonding 技能,实现两片晶圆堆叠的非存储类产品量产。

第二阶段:2021 年 M-stacking 技能量产,实现三层及以上的多片晶圆堆叠。

第三阶段:2022 年 Hi-stacking 技能量产,实现晶圆和 die 堆叠整合。

沈亮指出,第一阶段的 Hybrid Bonding, 越来越多地被客户青睐,用于“存算一体”类人工智能产品。同时在新兴的 d-TOF 上亦将发挥主要浸染,由于器件利用直接翱翔韶光测距,打算量哀求比传统 CIS 高,必须采取 Hybrid Bonding 连接方能达到更好的性能和用户体验。

第二阶段的多片晶圆堆叠 M-stacking 技能,是把 DRAM 晶圆也堆叠上去,可作为数据缓冲,实现对存储体的高速数据存取。现阶段采取后段封装工艺制造的 HBM,因其凸点工艺的局限,存在散热性能差、连接数少等先天弊端,影响存储容量和带宽提升空间。针对此问题,利用多片晶圆堆叠技能工艺精度高、连接热阻低和生产效率高的上风可大幅度提升性能。

第三阶段的 Hi-stacking 技能可供应晶圆和 die 堆叠在一起的多层办理方案,不再受高下 die 尺寸哀求同等的限定,从而使堆叠方案更灵巧,提升堆叠后产品的良率,降落产品本钱。

目前武汉新芯已经和多家客户开始以上项目的互助研发。