本文是专门为基于GD32 MCU开拓的工程设计职员供应,紧张先容了GPIO的功能配置、内部 构造以及在不同场景利用时的把稳事变,旨在帮助GD32 MCU开拓者优化对通用型输入输出端 口(GPIO)的利用,精确快速的利用GD32 MCU进行产品开拓。

GPIO,通用型输入输出端口的简称,可以通过软件配置其输出或者输入,GD32 的 GPIO 引 脚与外部设备连接,从而实现与外部通信,掌握以及旗子暗记输入的功能,是 GD32 MCU 中很常 见,利用最广泛的模块。

每个 GPIO 引脚可以由软件配置为输出(推挽或开漏)、输入、外设备用功能或者仿照模式。 每个 GPIO 引脚都可以配置为上拉、下拉或浮空模式或无上拉/下拉。

GD32 MCU GPIO 紧张特色有:

输入/输出方向掌握;

施密特触发器输入功能;

每个引脚都具有弱上拉/下拉功能;

推挽/开漏输出使能掌握;

置位/复位输出使能;

可编程触发沿的外部中断—利用EXTI配置寄存器;

仿照输入/输出配置;

备用功能输入/输出配置;

端口锁定配置。

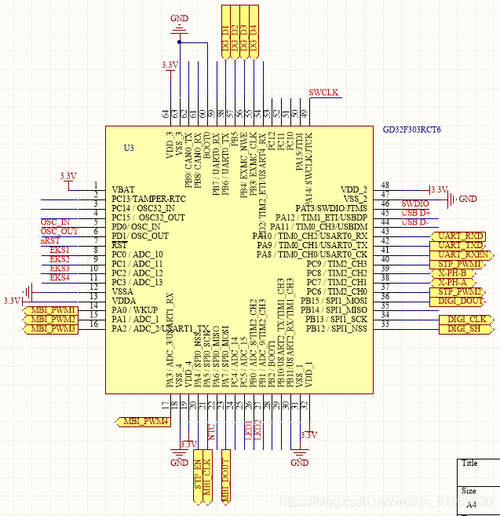

对付 GD32 某些系列 MCU 的 GPIO 可能具有更多功能,如时钟、I2C、SPI、CAN、USART、 USB、ADC、DAC 等,在进行电路板设计前应查看该系列的数据手册与用户手册,比拟所使 用的 GPIO 是否知足需求。

2. GPIO 构造

在 GD32 MCU 中,常日有两种类型的GPIO,非 5V 耐受IO 以及 5V 耐受 IO(部分MCU没 有 5VT引脚,如 GD32A503xx 系列),两种类型的IO 在构造上略有差异。

如图 2-1. 标准 IO 基本构造图所示为一个标准IO 口的基本构造图:

图 2-1. 标准 IO 基本构造图

I/O pin 表示的芯片的 I/O pad,与外部电路相连接,其他部分电路都是芯片的内部电路。

个中框图的上半部分表示 IO 的输出部分电路,当IO 利用其备用功能连接内部其他外设时,也 会共用干系功率输出部分电路。框图的下半部分表示 IO 的输入电路部分,作为备用功能连接 内部其他外设时,同样也会共用输入部分电路,如施密特触发器。框图的中间部分如红框4内 的电路表示仿照输入输出通道,仿照通道输出时(如 DAC 输出)不经由功率输出电路,输入 时也不经由施密特输入电路,直接将外部电路通过IO pin 与内部的仿照外设直接连接。

红框 3 表示的是 IO 输出时的紧张功率电路,配置干系的掌握寄存器,可以掌握上、下两个M OS 管导通以实现推挽输出或者是开漏输出。

红框 2 表示 IO 口的内部上拉或者下拉电路,通过干系寄存器的配置可以实现输入口的内部上 拉或者内部下拉,上拉/下拉电阻的阻值可以参考数据手册,范例值为 40kΩ,少数引脚高下拉 电阻非 40 kΩ,如 GD32F425xx 的 PA10 引脚高下拉电阻为 10 kΩ,详细数据可查看数据手 册中 GPIO characteristic 章节。

红框 1 中表示的 ESD 保护电路。

非 5VT IO 的 ESD 保护电路如图

2-2. 非 5VT IO 引脚基本构造图所示,ESD 保护电路在 IO 对 VDD 和 VSS分别形成两个二极管,显然,如果 IO 上的电压比 VDD 的电压大于二极管的正向 导通压降,或者IO 上电压比 VSS电位低,且压差大于二极管的正引导通电压,则会产生从IO到 VDD,或者从 VSS到 IO 的电流。

5VT IO 的 ESD 保护电路如图 2-3. 5VT IO 引脚基本构造图所示,5VT IO 引脚没有连接到电 源(VDD)的内部保护二极管。

因此,在实际利用中若存在引脚先上电,MCU 后上电的情形,优先选择利用 5VT的引脚作为 与外部连接先上电引脚,避免由于引脚泄电造成IO 引脚拉低;若必须选择标准IO引脚,需采 用比如三极管等隔离方法,防止引脚泄电。

图 2-2. 非 5VT IO引脚基本构造图

图 2-3. 5VT IO引脚基本构造图

图 2-3. 5VT IO引脚基本构造图

把稳:5VT IO 与非 5VT IO 内部构造有部分差异

3. 范例运用处景与把稳事变不同类型的 IO 在利用时有一些把稳事变,接下来分别从输入与输出两个角度来描述下不同类 型 IO 的范例运用处景与特性以及把稳事变。

3.1. IO 输入

首先是 IO 口的输入电压范围,输入耐压值表示 IO 口所能容忍的输入电压范围,部分 GD32 MCU 含有 5VT IO 与非 5VT IO,5VT IO 与非 5VT IO 有着不同的特性,如用户手册中的表 3-1. 绝对最大额定值所示。

表 3-1. 绝对最大额定值

针对 IO 口的输入场景,我们有几点须要把稳:

1. 对付 5VT IO,当 VDD=0 时(即 MCU 未上电时),其引脚输入电压不能超过 3.6V;

2. 我们须要根据 IO 口外部输入旗子暗记的电压值范围来慎重选择 5VT IO 还是非 5VT IO,如果 输入旗子暗记已经大于5.5V 了,就要将旗子暗记调理成适宜的范围再送到 MCU 的IO 口;

3. GPIO 输入低电平剖断范围为≤0.3 VDD ,GPIO 输入高电平剖断范围为≥0.7VDD ;

4. 根据前面描述不同类型IO 口的范例构造,如果非 5VT IO 上的电压比 VDD 电压大 0.3V 以 上,则会可能使 ESD 保护电路中IO 对 VDD 的二极管导通造成泄电,尤其是在 MCU未上 电,而 IO 口就已经有电平时的情景,此时,如果选择 5VT IO 可以有效规避从 IO 向 VDD 泄电的情形;范例的,如果IO 接入的是 I2C 总线,我们就须要选择5VT引脚;

5. MCU 所有的 IO 在上电完成还未进行其他配置时,均默认事情在浮空输入模式,个中调试 口为上拉或下拉模式,详细的上拉还是下拉请参照用户手册。因此,在一些须要产生固定 电平的场景中,如果 MCU 从待机模式复位,则须要考虑这些 IO 口的默认输入高下拉状 态,且在程序重新配置这些IO 的状态之前,默认状态不会变革;

6. 为了得到更低的功耗水平,尤其是在就寝模式和深度就寝模式中,须要将未利用的 IO 配 置成仿照输入,或者配置为浮空输入状态的同时外部加高下拉,或者设置为内部上拉或下 拉。需把稳设置内部上拉时,外部不可再硬件下拉,避免额外功耗,同理,内部下拉时, 外部不可硬件上拉(这里未利用的 IO 也包括在本封装上未引出来的 IO)。对付 GD32 低 功耗 MCU 产品,在运行模式下,如前描述的设置也会得到最好的功耗表现;

7. 5VT IO 只有在输入模式下才可输入最大 5.5V 电压。当输出模式被启用时,5VT IO 不再可 以承受 5.5V 电压。有关I/O 输入电压的详细信息,请参阅数据表通用操作条件表中的VIN 参数;

8. 只有在引脚上没有启用仿照功能时,5VT IO 才可输入最大 5.5V 电压。如果在5VT IO 上 启用了一些仿照输入功能(ADC 输入有源,COMP 输入,OPAMP 输入),那么引脚上的 最大事情电压不能超过min(VDDA, VREFP) + 0.3 V。

3.2. IO 输出在 IO 输出的场景我们也有一些要点须要把稳,

1. 开漏输出电压与输出带载电流有非常显著的关系,常日 IO 在输出高时,如果所带负载越 大,则输出的高电平就会被往下拉的越低,同理,如果 IO 在输出低时,流进 IO的电流越 大,则 IO 输出的低电平就会被往上拉的越高;

2. 对付 MCU 中存在备份域的型号,个中有部分 IO 是事情在备份域电源中的,这些 IO的带 载能力有限,建议这些IO 的 IO speed 参数设置为最低速率(一样平常为2MHz)。如 GD32F4xx 系列中的 PC13、PC14、PC15、PI8 四个引脚,不同系列驱动能力较弱的引脚不同,详细 信息可在该系列数据手册中查询;

3. GPIO 可通过电流与 IO 配置速率有关,目前所有 GD32 MCU IO 最大可通过电流均为25 mA(事情在备份域的引脚除外),GPIO 拉电流以及灌电流均不可超过 25 mA。当 GPIO 速率配置较低时,其拉电流与灌电流能力可能达不到 25 mA;

4. 部分 GD32 MCU 包含 I/O 补偿单元,如E50x 系列。默认情形下,I/O 补偿单元是不该用 的,当 I/O 端口输出速率大于 50MHz 时,建议利用 I/O 补偿单元对 I/O 端口进行斜率控 制,从而降落 I/O 端口噪声对事情电源的影响;

5. IO 在高低电平转换时过冲会随着 IO 口速率增大而增大,可通过降落 IO 口速率来减少过 冲;

6. GPIO 输出的高低电平并非绝对的零或者VDD,而会随着 IO 配置的速率、VDD电压、输出 电流的大小而变革。如表 3-2. GD32F425xx GPIO DC 特性所示为 GD32F425xx GPIO输 出高低电平随这些变量变革的数据表。

3.3. 其他把稳事变为了更好的提升 GD32 MCU 在一些范例运用处景下的性能,在利用 GD32 MCU 的 GPIO时 还需把稳以下事变:

1. 部分系列 GD32 MCU ADC 输入引脚为标准 IO 引脚,需把稳避免 ADC 输入电压超过 VDD+0.3V 的情形,否则可能由于泄电造成 ADC 采样非常;在利用 ADC 模块时,所有 ADC 引脚均不可引入负电压,否则将导致 ADC 采样不准;

2. VBAT引脚许可从外部电压源(电池或电容)为 GD32 备份域供电。当 GD32 微掌握器仅通过 VBAT引脚供电时,只有在备份域里的GPIO 才能事情。备份域的GPIO 驱动能力较弱,且 不同系列的备份域GPIO 不同,可在该系列的用户手册中查看。对付没有外部电池的运用, 建议将 VBAT引脚通过 100nF的外部陶瓷去耦电容接地后连接到 VDD 引脚上;

3. 为提高 EMC 性能,未利用的IO 口引脚建议硬件上拉或者是下拉;

4. 多组中同一标号 PIN 仅可配置一个 IO 口为外部中断,例:PA0、PB0、PC0 仅支持三个 中的个中一个 IO 口产生外部中断,不支持三个同为外部中断模式;