做为layout,只须要知道晶振是敏感器件,其本身易受滋扰同时产生的时钟也会滋扰别人;

而常日做法是:尽可能靠近芯片时钟脚;表层挖地,底下隔两层完全地层再走线;

其余晶振分一样平常常见四类:石英晶振,TCXO,VCXO[用到这个的要特殊把稳],OCXO,顾名思义呀,不一一先容;

然而在空间有限,叠层定去世,本钱压去世,性能许OK,不幸的是纠结与强制症一起呈现;

1.“尽可能靠近芯片时钟脚\"大众; 如果晶振是给pmu用的?如果晶振是给大功耗cup用?如果晶振已经尽可能靠近芯片时钟脚,不幸的是阁下刚好有大功率器件?

这就要分实际情形了,首先看“尽可能靠近”的本意是CLK走线只管即便短,少去麻烦他人,适用于其周围不存在温差变革大的和OCXO【存在极限值】;

2.“表层挖地,底下隔两层完全地层再走线”;

“表层挖地”的本意是隔离周围的热对晶振的影响,“底下隔两层完全地层再走线”的本意是晶振与两层下走线不要共地;避免引入噪声;然而晶振一样平常处于BGA的周围,下面满满的走线,隔两层就差强人意,因此就要分情形找紧张问题了;

如果两层下是一些电平掌握旗子暗记,常日是表层挖地,隔一层地;

如果两层下是一些通信口,总线,大电流途经,就必须担保晶振下两层完全地层,然而刚好BGA阁下有pmu或者pa;加层贵不可能,将tcxo换成OCXO贵弗成封装更大更加弗成,

这时候就只能捐躯“尽可能靠近”,移走,时钟旗子暗记做处理;

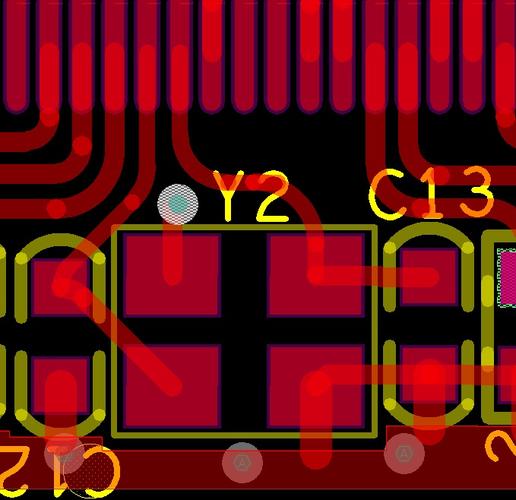

如下图;pmu阁下晶振的处理 :捐躯靠近,表层挖地,隔2层完全地后底下才走线;