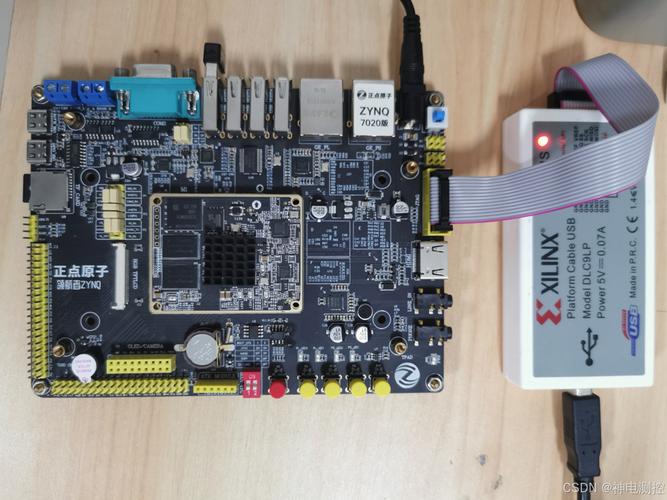

软件:Vivado2018.3,芯片型号:zynq7020系列

一、快速利用BlockDesign搭建一个带PS的FPGA工程

1. 打开Vivado2018.3后单击Create Project

2. 选择工程路径和输入工程名

3.一起Next,然后选择器件型号XC7Z020CLG400-2

4. 新建BlockDesign,在Flow Navidator工具栏内点击Create Block Design,并命名和选择路径(刚开始用默认即可)

5. Open Block Design 并添加zynqProcessing System模块,Diagram里面有加号可以加各种各样的IP到BlockDesign里面,可以右击空缺add ip,也可以用快捷键ctrl+i,实现功能一样

6. 设置PS外设,UART、Ethernet、和DDR3/4等,刚开始先可以只设置这三个就足够用了,后续根据功能再新增其他外设。双击zynq7 Processing System会弹出IP配置界面,点击对应的外设会直接跳到MIO Configuration里面去变动相应配置

(1)UART,根据事理图设置为EMIO还是MIO模式(大略理解EMIO便是PL透传引脚,MIO便是直接PS透传引脚),这里根据开拓板配置MIO14..15;

(2)Ethernet,本例程中网口芯片为Realtek RTL8211E,Processing System配置如下

(3)DDR3配置,DDR的配置也是根据器件型号和时钟频率来配置,比如型号MT41J256M16RE-125的DDR芯片processing system的配置如下,一样平常选好型号默认配置即可。

7. 设置完外设后,可以在根据需求引出一些时钟和复位旗子暗记,在Clock Configuration -> PL Fabric Clocks处设置,同样在PS-PL Configuration -> General -> Enable Clock Resets处设置复位旗子暗记。

8. 以上这是完毕后单击左上角的 Run Block Automation,牢记须要把M_AXI_GP0_ACLK接到FCLK_CLK0上,否则会报错。

9. 设置完毕后,找到Source,右击system,选择Create HDL Wrapper...-> Let Vivado manage wrapper and auto-update,然后就可以去Generate Bitstream,然后可以用2018.3 SDK工具来写嵌入式程序了。

10. 天生TCL,为什么要天生tcl脚本,由于在某些时候移植BlockDesign很麻烦,但是如果用tcl脚本来天生BlockDesign就很大略了。在Help阁下的搜索栏,输入export block design,并点击弹出工具栏,路径里面的tcl文件便是当前BlockDesign的所有连线和IP,后面想移植直接拷贝tcl文件就可以了。

后续:zynq系列之(二) --- 裸机掌握和Linux下掌握AXI GPIO和AXI BRAM,实现PS和PL的互通