为此,本人也是去考试测验了很多办理办法,一开始也没有去设想是JTAG口坏了。于是乎,本人换了usb-blaster,可一点反应也没有。难道真的是JTAG口坏了?后来,本人查阅干系资料,去搞清楚问题的实质在哪里。下面便是本人的一些收成,分享出来,仅供各位大侠参考,一起互换学习。

根据查阅资料及本人的一些实践履历所得,在利用JTAG下载接口的过程中,请不要随意带电插拔,否则会破坏FPGA芯片的JTAG口旗子暗记管脚。那么如何去确认JTAG口已经破坏了呢。

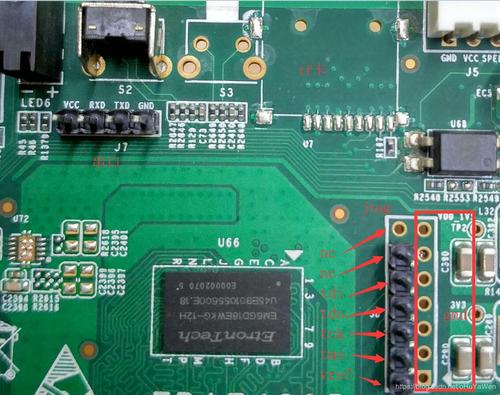

首先,你要去打消基本的几项成分,一是,是否匹配连接,有很多设备会对应很多接口,在实际条件下要匹配精确,否则也会涌现上述情形;二是,打消下载线的问题,如果是下载线坏了,可以利用多根下载线去考试测验,打消这类问题。如果还是不能访问FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已经破坏。此时请用万用表检讨TCK,TMS,TDO和Tdi是否和GND短路,如果任何一个旗子暗记对地短路则表示JTAG旗子暗记管脚已经破坏。

至于JTAG口是什么,这里我们也来磋商一下,JTAG英文全称是 Joint Test Action Group,翻译过来中文便是联合测试事情组。

JTAG是一种IEEE标准用来办理板级问题,出身于20世纪80年代。本日JTAG被用来烧录、debug、探查端口。当然,最原始的利用是边界测试。

一、边界测试

举个例子,你有两个芯片,这两个芯片之间连接了很多很多的线,怎么确保这些线之间的连接是OK的呢,用JTAG,它可以掌握所有IC的引脚。这叫做芯片边界测试。

二、JTAG引脚

JTAG发展到现在已经有脚了,常日四个脚:TDI,TDO,TMS,TCK,当然还有个复位脚TRST。对付芯片上的JTAG的脚实际上是专用的。TDI:测试数据输入,数据通过TDI输入JTAG口;TDO:测试数据输出,数据通过TDO从JTAG口输出;TMS:测试模式选择,用来设置JTAG口处于某种特定的测试模式;TCK:测试时钟输入;TRST:测试复位。

CPU和FPGA制造商许可JTAG用来端口debug;FPGA厂商许可通过JTAG配置FPGA,利用JTAG旗子暗记通入FPGA核。

三、JTAG如何事情

PC掌握JTAG:用JTAG电缆连接PC的打印端口或者USB或者网口。最大略的是连接打印端口。

TMS:在每个含有JTAG的芯片内部,会有个JTAG TAP掌握器。TAP掌握器是一个有16个状态的状态机,而TMS便是这玩意的掌握旗子暗记。当TMS把各个芯片都连接在一起的时候,所有的芯片的TAP状态跳转是同等的。下面是TAP掌握器的示意图:

改变TMS的值,状态就会发生跳转。如果保持5个周期的高电平,就会跳回test-logic-rest,常日用来同步TAP掌握器;常日利用两个最主要的状态是Shift-DR和Shift-IR,两者连接TDI和TDO利用。

IR:命令寄存器,你可以写值到这个寄存器中关照JTAG干某件事。每个TAP只有一个IR寄存器而且长度是一定的。DR:TAP可以有多个DR寄存器,与IR寄存器相似,每个IR值会选择不同的DR寄存器。

四、JTAG链干系疑问

打算JTAG链中的IC数目:一个主要的运用是IR值是全一值,表示BYPASS命令,在BYPASS模式中,TAP掌握器中的DR寄存器总是单bit的,从输入TDI到输出TDO,常日一个周期,啥也不干。

可用BYPASS模式打算IC数目。如果每个IC的TDI-TDO链的延迟是一个时钟,我们可以发送一些数据并检测它延迟了多久,那么久可以推算出JTAG链中的IC数目。

得到JTAG链中的器件ID:大多数的JTAG IC都支持IDCODE命令。在IDCODE命令中,DR寄存器会装载一个32bit的代表器件ID的值。不同于BYPASS指令,在IDCODE模式下IR的值没有标准。不过每次TAP掌握器跳转到Test-Logic-Reset态,它会进入IDCODE模式,并装载IDCODE到DR。

五、边界扫描

TAP掌握器进入边界扫描模式时,DR链可以遍历每个IO块或者读或拦截每个引脚。在FPGA上利用JTAG,你可以知晓每个引脚的状态当FPGA在运行的时候。可以利用JTAG命令SAMPLE,当然不同IC可能是不同的。

如果JTAG口已经破坏了,那只能“节哀顺变”了,但是也不要只顾着伤心,最主要的是剖析个中的缘故原由,做其他事情也是一样的道理。那我们就来剖析剖析,我们在利用的过程中,可能常常为了方便,随意插拔JTAG下载口,在大多数情形下不会发生问题。但是,仍旧会有很小的机率发生下面的问题,由于热插拔而产生的JTAG口的静电和浪涌,终极导致FPGA管脚的击穿。

至此,也有人疑惑是否是盗版的USB Blaster或者ByteBlasterII设计简化,去除了保护电路导致的。但经由很多实际情形的反馈,事实证明原装的USB Blaster 也会发生同样的问题。也有人提出质疑是否是ALTERA的低端芯片为了降落本钱,FPGA的IO单元没有加二极管钳位保护电路。这类质疑实在都不是办理问题的实质,最主要的是我们要规范操作,尽可能的去减少由于实际操作不当导致一些硬件设备、接口等提前结束寿命或“英年早逝”,那重点来了,关于JTAG下载口的利用,我们须要如何去规范操作呢。

上电时的操作流程顺序:1.在FPGA开拓板及干系设备断电的条件下,插上JTAG下载线接口;2.插上USB Blaster或者ByteBlasterII的电缆;3.接通FPGA开拓板的电源。

下电时的操作流程顺序:1.断开FPGA开拓板及干系设备的电源;2.断开USB Blaster或者ByteBlasterII的电缆;3.拔下JTAG下载线接口,并放置适宜地方存储。

虽然上述的操作步骤有点繁琐,有时我们在利用的时候也是不以为然,但为了担保芯片不被破坏,建议大家还是中规中矩的按照上述的步骤来操作。

本人上述涌现的问题,经由检测后便是TCK跟GND短路了,虽然发生的概率不是很大,但为了能够更合理更长久的的利用硬件干系设备,还是建议大家在实操过程中,不要担心繁琐,中规中矩操作,换个角度思考,“多磨多练”也是对自己有好处的。

图文来自“创易栈”