宽带射频事情频率范围为75MHz - 6GHz附带高效电源办理方案和时钟办理方案

官方版本是17的,本人目前只有166版本,委托网友给降了个版本,才能得以瞥见pcb,紧张从以下几点进行剖析,个人不雅观点,不喜勿喷!

1.射频走线设计

2.电源的走线/平面设计

3.时钟的走线设计

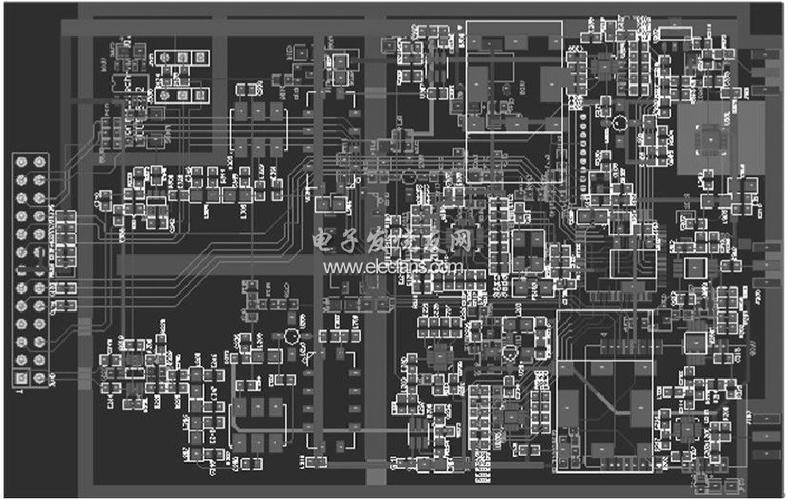

先来个见面照,top口试

然后展开看

1.射频走线设计

1)先瞅下实物图:

TOP

BOTTOM

可以清楚看到,射频线周围只剩“底裤”了,较宽的射频线周围是白白的东西(那是基材,拔了绿油的)

2)剖析射频线的阻抗

粗看阻抗线按照接地共面波导来管控的,及微带线和共面波导的结合形式

再详细阐明可以阅读下吴大神的阐明

https://www.mr-wu.cn/gauge-effects-coplanar-ground-planes/

测线宽:15.5mil

车间距:20mil

看层叠:第二层没有挖空

好模糊,没办法,pcb 这层彷佛比例不折衷--

补充一个数据手册上面的:

阻抗解释

阻抗线是按照阻抗解释设计的,线宽是15.5mil

这个可以利用polar 打算器验证下 ,我就不打算了

这里两个细节:

a】把阻抗线上面绿油去了

b】表层的gnd铜皮间隔阻抗线大于阻抗线宽的

2.电源设计

art03

art12

来个合照:

总结:

1、线宽大概是11mil 25mil 30mil

2、这几路电源大都对应一个bga ball或者2个,没有很多

3、这种adc对电流哀求不是很高,但是隔离度哀求非常高,如art12层电源层险些是全包围构造了

电源是否干净决定了单板的出身啊!

3.高速串行总线:JESD204B

a、204b的阻抗掌握

建议:掌握单线50欧姆,差分线松耦合来掌握差分100欧姆,间隔便是5mil/15mil

走线阻抗:

走线之间的隔离度:

沿途打过阵列:

过孔直接间距:

端过孔处理: