下面就给大家先容一下几种常见的CPU架构:

X86

1978年6月8日,Intel发布了史诗级的CPU处理器8086,由此X86架构传奇正式拉开帷幕。首次为8086引入X86作为打算机措辞的指令集,定义了一些基本利用规则,X86架构利用的是CISC繁芜指令集。同时8086处理器的大得胜利也直接让Intel成为了CPU巨子,如果你对8086不是那么熟习,那么一定听过奔驰处理器吧?况且为了纪念8086K出身40周年,今年Intel发布了一颗纪念限量版的处理器Core i7-8086K,这你都听说过吧?

来自Intel官网

图片

IA64(Intel Architecture 64,英特尔架构64)

哇,IA64听起来好陌生,是的,虽然同出Intel之手。但这可以说是失落败品。当年X86过渡到64位指令集时,一个欠妥心被AMD弯道超车,末了只能联合惠普推出了属于自己的IA64指令集,但这也仅限于做事器上,也是Itanium安腾处理器的来历(现在已经凉了)。

图片来自x86-guide

至于IA64究竟是RISC还是CISC指令集的延续,这个真的很难说清楚,但纯挚以IA64基于HP的EPIC(Explicitly Parallel Instruction Computers,精确并行指令打算机)来看,彷佛更倾向于RISC体系。

MIPS(Microprocessor without interlockedpipedstages,无内部互锁流水级的微处理器)

在上世纪80年代由美国斯坦福大学Hennessy教授的研究小组研发,它采取精简指令系统打算构造(RISC)来设计芯片。和Intel采取的繁芜指令系统打算构造(CISC)比较,RISC具有设计更大略、设计周期更短等优点,并可以运用更多前辈的技能,开拓更快的下一代处理器。MIPS是涌现最早的商业RISC架构芯片之一,新的架构集成了所有原来MIPS指令集,并增加了许多更强大的功能。MIPS自己只进行CPU的设计,之后把设计方案授权给客户,使得客户能够制造出高性能的CPU。

让MIPS出名的,可能是在2007年,中科院打算机研究所的龙芯处理器得到了MIPS的全部专利、指令集授权,中国开始走上了一MIPS为根本的CPU研发道路。

图片来自龙芯官网

PowerPC

PowerPC是有蓝色巨人IBM联合苹果、摩托罗拉公司研发的一种基于RISC精简指令集的CPU,PowerPC架构最大优点是灵巧性非常好,核心数目灵巧可变,因此在嵌入式设备上具有很高效益,可以针对做事器市场做超多核,针对掌机做双核,因此它具有精良的性能、较低的能量损耗以及较低的散热量。

图片来自wikimedia

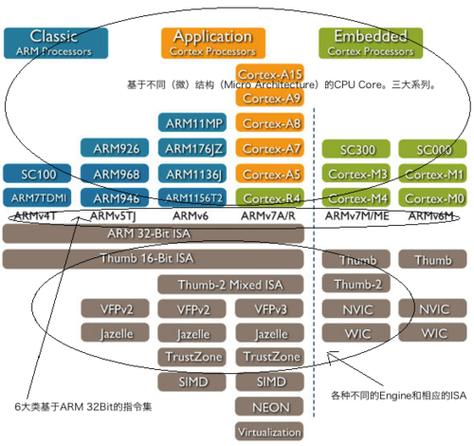

ARM(Advanced RISC Machine,进阶精简指令集机器)

ARM可以说是一个异军突起的CPU架构,采取了RISC精简指令集,而且ARM发展到本日,架构上非常灵巧,可以根据面向运用处景不同利用不同设计的内核,因此可以广泛用于嵌入式系统中,同时它高度节能的特性,目前各种移动设备中全都是它的身影。据统计,利用ARM架构的芯片年出货量高达200亿片,随着物联网时期降临,对付低功耗性ARM芯片需求量会发生爆炸性增长。

图片来自iFixit

CISC、RISC之争

从上面得知,历史的长河里面,有过许许多多的CPU架构,它们之间的差异性非常大,经由韶光、用户的考验,我们平常所打仗到CPU架构也就剩X86和ARM两者,按照最核心的不同可以被分为两大类,即“繁芜指令集”与“精简指令集”系统,也便是常常看到的“CISC”与“RISC”。

要理解X86和ARM CPU架构,就得先理解CISC繁芜指令集和RISC精简指令集 ,由于它们第一个差异便是X86利用了繁芜指令集(CISC),而后者利用精简指令集(RISC)。造成他们利用不同该指令集的缘故原由在于,面向的设备、工具、性能哀求是不一样。手机SoC普遍都是采取ARM供应的核心作为根本,依据自身需求改变SoC的核心架构,而ARM正正是RISC精简指令集的代表人物。CPU巨子Intel、AMD所采取的X86架构已经沿用了数十年,是CISC繁芜指令集的范例代表。

CISC繁芜指令系统便是为了增强原有指令的功能,设置更为繁芜的新指令实现部分大量重复的软件功能的硬件化。由于早期的电脑主频低、运行速率慢,为了提高运算速率,不得已将更多的繁芜指令加入到指令系统中来提高电脑的处理效率,逐步形成以桌面电脑为首的繁芜指令系统打算机。其指令集也是在不断更新增加当中,如Intel为X299平台上的处理器增加了AVX 512指令集,目的便是为了提高某一方面的性能。

虽然CISC可以实现高性能CPU设计,但是设计起来就相称麻烦了,要保持弘大硬件设计精确是一件不随意马虎的事情,还要确保性能有所提升,不能开倒车,因此桌面CPU研发韶光也逐步地变长。这时候,以ARM为首的一些RISC精简指令系统打算机开始崭露锋芒了。

RISC可以说是从CISC中取其精华去其糟粕,简化指令功能,让指令的均匀实行周期减少,达到提升打算机事情主频的目的,同时引入大量通用寄存器减少不必要的读写过程,提高子程序实行速率,这样一来程序运行韶光缩短并且减少了寻址,提高了编译效率,终极达到高性能目的。

这两种指令集一贯都在求同存异当中,都在追求在体系架构、操作运行、软硬件、编译韶光以及运行韶光等等诸多成分中做出某种平衡,以此达到当初所设计的高效运转目的。

图片来悛改浪博客

功耗上的限定

从CISC、RISC设计思路来看,大家不难创造,他们走的路根本不一样,前者专注于高性能方向,但带来高功耗,而后者专注于做低功耗的嵌入式,对付性能的最强不是太过强劲。因此我们也看到Intel、AMD他们善于于设计性能超高的X86处理器,而高通、苹果依赖ARM IP授权设计出看重效能的SoC芯片。

就像我们以前所举的例子,Core i7-8086K可以轻易跑出95W功耗,但像高通骁龙845这种最顶级的SoC也不过是5W,只有其1/19,紧张是手机尺寸越来越小,电池容量、能量密度发展跟不上,手机所用ARM内核只能是低功耗。

一样平常来说,处理器的功耗可以随着制造工艺的进步而降落,但近些年来,移动设备所采取的的SoC每每率先利用更小的纳米工艺制程,比方说骁龙845的10nm,虽然里面有取巧身分,但推进速率远远快于Intel的10nm工艺,加之SoC还会有对应的低功耗版本工艺,以是无论是设计上、还是工艺上的差别,都导致了ARM、X86功耗差异非常大。

大小核架构

从前的X86传统CPU,如果是四核或者是双核,内部的四个、两个个核心都是千篇一律的,这样的话,由于一旦软件只能调度一个核心,处于高频事情,但由于架构限定,别的核心也要保持同样的高频率和高电压状态,这样就摧残浪费蹂躏了大量的能量在做无用功。后来就发展出了异步多核,许可不同核心事情在不同频率上,以此换来更低功耗。

由于移动设备更加在意功耗,以是ARM采取了更加激进的做法,八个核里面许可有不同Cortex-A架构核心,那便是著名的ARM bigLITTLE。这样的大小核设计目的很明确,便是在有限的电池容量中,兼顾性能、续航的需求,因此SoC内部的CPU是采取异构打算,既有高性能大核心,也有低功耗小核心。

bigLITTLE架构框架,图片来自ARM官网

芯片设计厂商可以根据自己的需求,设计出有针对性的产品,比方说目前高通骁龙845、华为的麒麟970、联发科Helio X30都是bigLITTLE架构,这样的话如果你只是刷刷微博、朋友圈,那么只须要动用小核心就能完成任务,玩《绝地求生》吃鸡游戏就可能大小核全开,从而担保性能、续航的平衡。

因此ARM的bigLITTLE异步多核架构非常值得参考,乃至传闻称英特尔将在第10代酷睿处理器Lakefield上利用这种技能,高性能大核是Ice lake(下一代Core),低功耗小核心则是Tremont(下一代Atom),因此在整体功耗上掌握在35W以内,用于二合一条记本上。

ARM、X86也能相互领悟

之前我们在另一篇超能教室《手机SoC与电脑的CPU性能究竟差多少?》就总结过,RISC、CISC各有各的上风,目前两者界线开始逐渐变得模糊,当代的CPU每每采取了CISC的外围,而内部则加入了部分RISC的特性,这个也是Intel处理器的开始拥有RISC的范例例子。也便是说实在未来CPU发展方向之一便是领悟CISC以及RISC,从软件、硬件上取长补短,进一步提高处理器的并行性以及工艺水平。

X86、ARM在性能、功耗上各占上风,只管ARM一贯想进入高性能做事器市场上,但一贯都是雷声大雨点小,前不久想要寻衅intel做事器地位的高通,ARM做事器部门直接裁员50%,技能副总裁也不玩了;ARM处理器也期望能得到X86处理器的高性能,以便能用在移动条记本上,就像刚刚推出的高通骁龙835 Windows条记本一样,但评价、反响都是平平;Intel利用X86架构Atom做手机SoC,结果还是败给了ARM,亏掉数十亿美元,终极直接砍掉了这个项目,老诚笃实做X86处理器。

以是说ARM、X86都在各自领域站稳了脚跟,由于设计之初的理念不同,已经很难渗入对方的领域,只能说不断考试测验,两者之间的差异在将来可能会缩小,不断借鉴改进。

图片来自esa-automation