正如SemiWiki的Daniel Nenni在一篇文章中所述:“(此前)Mentor 的系统级方案比 Synopsys 和 Cadence 要少,因此处于劣势。此外,Synopsys 和 Cadence 的收购策略也比 Mentor 更激进。”但“随着西门子的到来,统统都发生了改变。”

西门子是环球最大的电子电气工程办理方案公司,2021财年的年发卖超过600亿美元,(Synopsys 和 Cadence 的总收入约为 亿美元)。也恰是以,西门子被Daniel称为“绝对是 EDA 游戏规则的改变者。”

西门子目前在软件领域投资已超110亿欧元,在工业软件和自动化市场均排名第一,西门子EDA正属于西门子的数字化工业集团旗下的数字化工业软件部门。

如今,间隔这次收购已经由去数年,芯片市场发生了很多变革,那么EDA将如何应对这一系列的变革?西门子EDA环球副总裁兼中国区总经理凌琳和西门子EDA亚太区技能总经理李立基以西门子EDA为例,详细讲述了数字化浪潮下,EDA技能和家当的发展动向。EDA行业正在通过结合AI与云的能力,从而知足芯片繁芜性寻衅,以实现从芯片到系统的扩展。

EDA的发展:下一代系统设计平台

为了不断推进IC家当发展,西门子EDA紧张环绕三方面进行改造,分别是实现更前辈的工艺技能,实现设计规模扩大以及实现系统规模扩宽。

正如西门子EDA集成电路部门实行副总裁Joseph Sawicki在日前召开的User2User大会中所说,摩尔定律并没有完备去世掉。以苹果A系列处理器为例,从2013年到2021年间,晶体管数量从10亿增长到了150亿,单核Geekbench的分数也从269提高到了1734,但是Dennard scaling(登纳德缩放比例定律)已经失落效——时钟频率并没有提高16倍。

此外,无论是英特尔、台积电以及ASML,家当链的各代表公司都给出了未来的路线图,也恰是以对付EDA而言,须要不断知足新工艺节点的哀求。比如,西门子EDA的Calibre nmPlatform IC签核实体验证办理方案,Analog FastSPICE平台,Aprisa数字实例办理方案等都得到了台积电N5、N4、N3等前辈制程认证,并作为定制化设计参考流程(CDRF)的一部分。

其次,是设计规模的不断扩大。为了缓解延迟,单芯片的尺寸正在不断增加。此外,包括Chiplet、2.5D/3D异构集成等技能不断呈现,使得设计规模不断增加。在这种情形下,就须要更新的设计方法论。李立基阐明道,比如两个点之间的检讨,便是一条线,三个点是三条线,四个点就要对应六条线,可以说繁芜度呈现指数级增长。如果是开拓一颗面积增加一倍的芯片,理论上须要四倍于现有资源。

实现系统规模的扩展是西门子EDA第三个发展方向。从 1992 年到 2014 年,半导体在电子系统中的份额为 16%,但现在已增长到 24% 旁边,并且预测显示,到 2025 年,电子系统的收入将达到 3.2万亿美元,因此对应的半导体市场规模可见一斑。也恰是以,系统公司正在切入IC领域,以实现更多的差异化。苹果、亚马逊、谷歌、复兴、特斯拉、博世、华为、Facebook等公司都是如此。代工厂客户中的系统公司收入占比已经从 2011 年仅占收入的 1% 增长到 2021 年的 21%,个中苹果已成为台积电的第一大客户。 此外,在 2006 年的 Hot Chips 会议上,只有 16% 的被接管论文来自系统公司,而到 2021年,这一数字已增长到论文的33%。因此,也可以看出系统公司正在推动芯片设计的创新。

李立基以西门子EDA较新的三个范例工具代表,解读了公司的三个发展方向。个中有新推出的专注稠浊旗子暗记验证的Symphony Pro,有去年推出的电源完全性剖析工具mPower以及2019年推出的自动驾驶硅前验证环境PAVE360。

除了不断追求更高制程之外,稠浊旗子暗记芯片设计也正变得越来越普遍。根据 IBS Research的数据,如今在物联网、通信、汽车和工业掌握领域,85%的设计是稠浊旗子暗记。这也是Symphony Pro平台推出的最直接缘故原由,基于原有的Symphony稠浊旗子暗记验证能力,进一步扩展功能,以全面、直不雅观的可视化调试集成环境支持新的Accellera标准化验证方法学,使得生产效率比传统办理方案提升多达10倍。

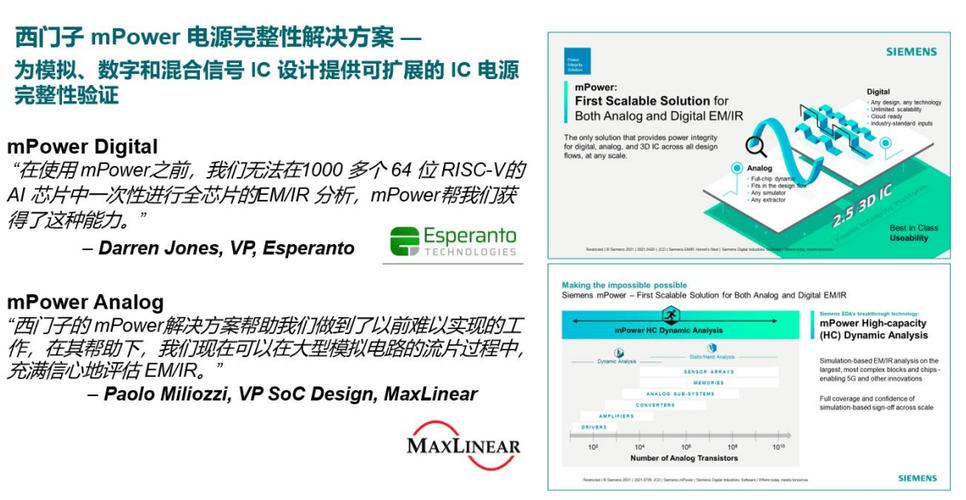

除了数模稠浊之外,电源完全性也成为了如今大规模芯片设计中的难点。mPower可通过分布式打算,供应近乎无限扩展性的IC电源完全性验证解決方案,即便对付最大规模的2.5D/3D IC设计,也能够实现全面的电源、电迁移(EM)和压降(IR)剖析。

PAVE360则是为下一代汽车芯片的研发供应的跨汽车生态系统、多供应商协作的综合环境,使数字化双胞胎(digital twin)仿真不但局限于处理器,还包括汽车硬软件子系统、整车模型、传感器数据领悟、交通流量的仿真,乃至还仿真自动驾驶汽车终极在智能城市里面的驾驶。李立基先容道,在PAVE360中,不只包含西门子EDA的硬件加速器,也包括西门子数字化工业的其他软件,通过机器、软件、芯片的紧耦合,可确保在知足ISO 21448安全认证的条件下,加速自动驾驶系统构建、软件验证及芯片开拓的周期。

实际上不止汽车,目前各行业中的芯片、软件和系统的耦合程度都越来越高,开拓正在不断左移,也恰是以须要更多的仿真、验证及数字孪生技能,并许可软件、机器和芯片同时开拓。为此,西门子EDA的下一代系统设计平台,将紧张通过五个方面,为从芯片到PCB再到系统,助力客户的数字化,分别包括数字化集成;搭建系统级设计的观点和技能;数字虚拟原型验证;基于模型的工程设计以及弹性供应链。

AI正在加速芯片开拓效率

随着芯片规模不断增长,芯片设计本钱越来越高,7nm的本钱要高达2.8亿美元。为了节省设计和验证本钱,一个较好的方法是利用须要更高阶的措辞及更新的设计方法论,比如从RTL向System C过渡。以NVIDIA为例,2019年8月在Hot Chips上,展示了一个只有10名工程师的小团队在6个月内通过利用C++和HLS(高等综合)方法,就开拓了一颗深度学习推理加速芯片的新方法。

除此之外,人工智能也是EDA改进效率的一个主要武器,西门子EDA也利用了很多AI干系知识以提高效率。李立基表示,比如Solido可利用机器学习快速进行特色向量库的天生和提取,以更少的韶光实现更高的验证精度,并将所得数据以可视化办法呈现;Tessent测试与良率提升工具可供应诊断驱动的良率剖析(DDYA)方法,贯穿产品生命周期的完全测试,利用物理版图数据来改进测试和良率剖析,可将创造良率丢失根本缘故原由的周期韶光缩短75~90%;Calibre SONR将Calibre机器学习模型与核心Calibre架构集成,以提高晶圆厂毛病检测和诊断的生产力和准确性,在这个中OPC(光学临近效应检测)受益最多。此前OPC须要海量的数据建模,并须要上万颗CPU进行打算,而通过AI和机器学习,极大简化了OPC的打算。

利用云打算提升灵巧性

凌琳表示,前辈工艺开拓本钱不断提高,系统越来越繁芜,须要调动更多的资源,这个中包括工程职员,同时也包括软硬件的打算资源,License资源等等。云上EDA可以灵巧分配资源,从而办理设计过程中的关键瓶颈。

目前西门子EDA可以供应五个方面的云做事,分别包括Cloud Ready、Managed Cloud(云管理)、Cloud Connected(云联接)、Cloud Native(云原生)以及Veloce云。

2019年,AMD工程师利用西门子EDA供应的经台积电认证的Calibre nmDRC软件平台在约10小时内完成了对其最大的7nm芯片设计—Radeon Instinct Vega20—的物理验证。该验证过程通过利用由AMD EPYC处理器驱动的HB系列虚拟机在Microsoft Azure云平台上运行完成。

拥抱家当与生态系统

西门子EDA一贯在伴随着中国的集成电路家当、客户以及互助伙伴共同发展。凌琳给出了一些主要韶光点,1989年Mentor Graphics进入中国,成为首家进入中国市场的EDA公司;1994年,时任Mentor CEO Walden C. Rhines来到中国参加EDA Tech Forum,这也是最早的EDA开拓者大会;1997年景立上海办事处并于2002年升级为中国区总部,此时凌琳等一批骨干加入,并一贯事情至今,2009年上海成为了Mentor亚太区总部。这二十年来,通过不断完善领导班子和核心成员,构建了立足中国扎根中国的EDA供应商。“我们的员工大多数都很稳定,以至于业内很多人都说过西门子EDA的人很长情,这也是我们的一个基因和特色。”凌琳说道。

人才不止是EDA公司关注的财富,更是如今IC家当界的所需。据《中国集成电路家当人才白皮书(2019—2020年版)》测算:到2022年前后我国全行业人才需求将达74.45万人旁边,缺口达25万之多。

凌琳表示,西门子EDA很早就意识到校企产学研共同互助来培养IC领域的人才,这也是中国IC家当的基石,为此,Mentor于1991年、1993年、2004年陆续和清华大学,复旦大学和北京大学签约国家重点实验室项目,并与教诲部签署了《集成电路人才培养操持》。

2018年,西门子EDA加入到中科院和教诲部成立的示范性微电子学院产学领悟发展同盟,并投入各种资源,帮助27所示范微电子学院进行课程培训,与教授开展课程同盟等事情。截至目前,西门子EDA同超过80家的大学有互助操持。

除了高校,西门子EDA也同中国的客户进行多项培训互助。“我们曾经在上海办公室连续三年开设了四至六周的专训班,帮助本土半导系统编制造商培养了五六十名专业的打算光刻和OPC人才,为行业解困,支撑行业发展。”凌琳说道。

除理解决人才培养问题之外,西门子EDA也致力于加速各生态系统的培植,以促进标准的盛行。比如为理解决Chiplet的模型标准与沟通,Chiplet Design Exchange (CDX) 作为一个OCP(开放打算项目基金会)的事情组而成立。CDX 的成员来自 EDA、chiplet 供应商和系统级封装技能的终极用户,西门子EDA就在个中,并揭橥了《用于异构集成的标准化Chiplet模型》的白皮书。

要走得更远

在收购Mentor之后,西门子EDA又陆续完成了十次收购,以补全EDA家当链。“西门子EDA是西门子数字化工业软件中不可或缺的一部分,可以帮助西门子数字化工业软件形成更完全的闭环。从电子、电器、机器、热能、嵌入式软件到更大技能领域的设计、制造和生产。同时,还包括更多流程管理软件,从产品、制造、设计、仿真到产品线的方案一应俱全。我相信这是大企业的诉求,也只有西门子EDA这样一个完全的平台可以知足这些诉求。”凌琳说道。

除了为客户供应整体办理方案,加速客户生产力之外,西门子EDA也在力求帮助芯片公司更好地节约本钱。李立基表示,EDA的实质便是通过自动化工具改进开拓流程,这和西门子公司所倡导的提升体验,加强工业化效率相同等。凌琳也表示,摩尔定律的实质便是经济效益,EDA可以帮助芯片不断降落本钱,这个中包括了设计、生产和测试的全流程。

凌琳援引西门子创始人维尔纳·冯·西门子的一句名言——“绝不为短期利益而捐躯未来。”为了实现工业变革和科技变革,西门子EDA要考虑得更远。