(西安理工大学 自动化与信息工程学院,陕西 西安 710048)

择要:本文紧张从视频图像采集系统出发,针对基于FPGA视频采集系统中须要实时显示和高效存储视频数据的问题,设计了视频解码和SDRAM存储模块。在全体系统中利用CCD摄像头将采集到的仿照旗子暗记经解码芯片ADV7181B解码后,转换为数字旗子暗记,并利用乒乓存储方法存储在SDRAM中,以方便供应给后期其他操作。在剖析了视频解码及SDRAM的基本事理和紧张参数的根本上,利用Verilog措辞实现了将有效视频数据分离出来并串行输出,同时也将图像分辨率调度为符合VGA显示的像素大小。另一方面通过乒乓缓存也担保了实时性、高速率的数据存储。末了,经由Modelsim仿真验证,证明了本设计的有效性。

0弁言

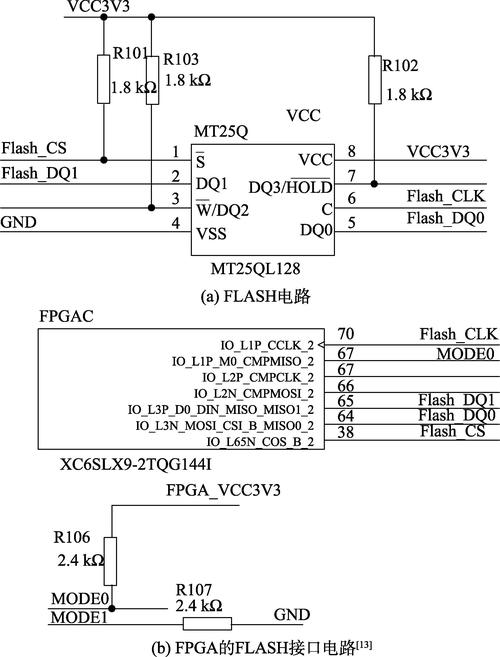

图1视频采集系统框图视频图像采集系统运用非常广泛,随着打算机通信技能的不断发展,FPGA以其高性能、低开拓本钱等优点广泛运用于视频和图像处理领域[1],因此,更加深入地研究基于FPGA的实时图像采集系统, 对付视频监控系统、高性能的图像处理等都具有极其主要的浸染。本文紧张研究的内容是基于FPGA的视频采集及显示系统中的视频解码和视频数据存储的问题,对付提取有效视频数据流和高效实时存储大量数据具有显著性的意义。

1视频图像数据采集系统的总体架构

图1为视频图像采集的系统框图,紧张由I2C配置模块、ITU656视频解码模块、SDRAM掌握器模块、视频格式转化模块和VGA掌握器模块组成[2]。为了使视频数据能实时、高速的显示,视频解码模块和SDRAM掌握模块就显得尤为主要。

2ITU-656解码

ITU-656是国际电信同盟制成的视频标准,是国际电信同盟建议为实现在专业视频设备之间传输BT.601标准、4∶2∶2的YCrCb数字视频旗子暗记而定义的一个并行接口和一个串行接口。个中,并行接口在传输4∶2∶2的YCrCb视频数据流的同时,也会输出水平同步旗子暗记HS及垂直同步旗子暗记VS掌握。

本文中ITU656标准的视频数据以27 MB/s的速率按Cb,Y, Cr,Y, Cb,Y, Cr,…的顺序分时传送[3]。个中,Cb,Y,Cr是同一个地址的亮度和色差旗子暗记,Y对应于下一个亮度采样旗子暗记。 Y采样频率为13.5 MHz,Cb采样频率是6.75 MHz,利用8位PCM编码表示每个采样点。ITU656 标准的数据传输格式如图2所示,每行采样1 728个样本点,个中Y为720个,Cb,Cr各360个。消隐期间的数据为288个(包括EAV和SAV)。

行掌握旗子暗记有两个定时基准旗子暗记:SAV和EAV。 EAV和SAV之间有280个固定填充数据。 SAV和EAV具有相同的前同步码:FF,00,00,而后面的XY决定着该行在全体数据帧的位置,并且SAV和EAV旗子暗记可以通过XY的值来差异,同时XY也包含有奇偶场识别、状态和信息、场消隐行消隐状态。

F:F=0奇场,F=1偶场;V:V=1消隐数据,V=0有效行数据;H:H=0表示SAV,H=1表示EAV;P3,P2,P1,P0:保护比特位,其值由F、V、H 决定。

ITU656数字解码模块[4]的功能是根据ITU656视频数据流的特点将有效视频数据YCbCr和F、V、H 掌握旗子暗记分离开来,并通过打算像素行列的坐标,确定图像中像素的详细位置,根据ITU656数据传输时序,通过行内计数办法去除行消隐数据,并分离出SAV、EAV 旗子暗记,留下只包括YCbCr旗子暗记的数据流,并将其串行输出。ITU656数字解码模块另一个功能是通过打算水平数据的像素坐标,将图像分辨率由720×576调度为640×480,以便在VGA中显示。

根据SAV 和EAV 都因此FF、00、00 的顺序开始的特点,设置一个序列移位器,采取4级寄存器级联的形式,每个寄存器缓存8 bit数据,并监测后面3个寄存器的值,当这三个寄存器缓存的数据不是FF、00、00时,序列移位器向右移,当检测到这3个寄存器的值为FF、00、00、时,即认为是SAV或EAV的到来,就将第一个寄存器的 bit6、bit5、bit4分别存放到3个一位寄存器中,从而提取出 F、V、H 旗子暗记。H(bit4)如果为0,即表示有效数据开始。再通过 V、F是否为0可判断出是有效行数据还是消隐数据,是奇场还是偶场的数据。解码过程如图3所示。

调度图像分辨率,定义一个Active_Vedio旗子暗记,如果Active_Vedio在0~1 440之间,则为有效视频数据。首先720行数据调度为640行数据,把SAV和EAV旗子暗记提取出来后,此处设计一个FVAL旗子暗记,如果FVAL为1,则得到一行720个有效像素值,因此要在这720个有效像素中裁剪掉80个像素。本设计利用Verilog措辞,水平方向的像素提取用一个除法器iskip来实现,定义一个水平计数器OTY_X,即除法器iskip=OTV_X%9,若iskip为0,则该像素点被丢弃,否则保留。在丢弃像素点时遵照两个原则[5]:(1)像素数据为只包含亮度信息的像素点,则将此像素点的亮度值Y丢弃,并且将上一个像素点的色度分量Cr同时丢弃;(2)像素数据为一个完全的像素点,包含了Y、Cb、Cr分量值:将分量Y和Cb丢弃,保留Cr;其次576行数据调度为480行数据,根据PAL制式视频旗子暗记的特点,分别取偶数场24~264行240个数据,奇数场312~552行240个数据,组成480行VGA数据,其他数据丢弃,由于丢弃的仅是一副图像的最边缘部分,以是对整幅图像影响不大。

提取有效视频数据,PAL制式的视频旗子暗记的场消隐一共是49行,个中偶数场和奇数场的消隐期分别为24行和25行。通过设计一个4位行计数器TY_Y实现,当Hs=1时对Vs进行计数,如果YV_Y大于或即是24,就可以输出稳定的有效视频数据。

解码模块如图4所示。

图5是ITU656 数字解码模块在Modelism6.6中的仿真图,图中TD_DATA是输入的视频流,当它涌现FF0000同时XY中的H、V 都为0时,开始输出有效的视频数据,输出旗子暗记oYCbCr的高8 位为Y,低8位为Cb和Cr交替涌现。

3SDRAM掌握器设计

视频采集模块中,采取ITU656同步时钟27 MHz,而SDRAM的事情时钟常日在100 MHz以上。为办理读写时钟不同步的问题,本设计中,采取了四个异步FIFO[6]用于跨时钟域的同步化,其浸染是将CCD摄像头采集进来的图像数据进行缓存,通过写FIFO读入SDRAM,读FIFO输出给VGA掌握器。读写FIFO是利用FPGA的片上资源从IP核中调用过来的,将SDRAM的数据端口仿真成四个虚拟端口(两个写端口两个读端口),掌握器根据缓存FIFO的状态对SDRAM发出读写要求,采取页模式突发传输和Bank切换的办法来匹配时序哀求。

异步FIFO的宏模块设计如图6所示。

图6FIFO宏模块 SDRAM 本身要进行刷新、预充电等操作,不能时候处于传输数据的状态,而且掌握逻辑比较繁芜,不能和其他器件进行透明连接,为此,设计一个 SDRAM掌握器,其他模块就可通过 SDRAM掌握器模块接口和 SDRAM 相连接,从而对 SDRAM 进行操作,实现乒乓缓存。

本文设计的SDRAM掌握器[7]紧张由系统读写掌握模块、SDRAM掌握接口模块、命令解析相应模块、数据通道模块组成,其内部构造如图7所示。

(1)系统读写掌握模块

该模块的功能是与外设接口相连,接管外部发来的掌握旗子暗记,并对掌握旗子暗记进行编码。根据FIFO的空满状态发出对SDRAM的读写要求旗子暗记。当写FIFO里面所存储的数据大小为SDRAM一页数据时,则写FIFO通过读要求旗子暗记往SDRAM里面传输数据。由于每个端口FIFO里面可以缓存两页大小的SDRAM数据,以是当写FIFO向SDRAM里面传输数据时也可以连续缓存输入进来的图像数据。同理,当VGA掌握器向读FIFO读取数据时,读FIFO里面缓存的数据大小小于SDRAM每页的大小时就可以进行读出了,此时SDRAM也可以连续向读 FIFO里面缓存数据。以此轮流进行缓存操作。

(2)SDRAM 掌握接口模块

该模块紧张完成初始化功能以及剖析系统指令。初始化结束后,系统开始吸收并剖析指令旗子暗记和地址信息,同时还要剖析来自命令模块的CMD_ACK反馈旗子暗记,并产生相应的SADDR信息给命令相应模块。

(3)命令解析相应模块

该模块接管来自SDRAM掌握接口模块的指令并进行判断,根据发来的指令产生对SDRAM进行掌握的旗子暗记:地址旗子暗记(ADDR)、掌握旗子暗记(CS、CKE)和指令旗子暗记(RAS、CAS、WE)。此外,可以通过LOAD-MODE命令,对预设的模式寄存器进行配置,从而实现对SDRAM事情模式的操控。末了,该模块通过使能旗子暗记OE来判断读、写要求旗子暗记,以此来掌握数据通路模块数据的发送方向。

(4)数据通路模块

数据通路模块的功能是:在写数据时将输入的数据送入到SDRAM中或者在读数据时将SDRAM中的数据送到数据输出口。

SDRAM掌握器的顶层模块如图8所示。

设计好 SDRAM掌握器后,采取2个SDRAM,利用乒乓缓存[8]构造的办法来实现对视频旗子暗记的缓存。在第1个缓存周期,输入的数据流在SDRAM掌握器掌握下被写入到SDRAM1中。在第2个缓存周期,通过选择旗子暗记的切换,将输入的数据流写入到SDRAM2中;同时,将SDRAM1中写入的第1个缓存周期的数据读出,输出到运算处理单元进行处理。在第3个缓存周期,再次通过选择旗子暗记切换数据的输入与输出缓存单元。如此循环,从而将缓冲的数据流一直顿地送到下一模块进行处理。

图9为SDRAM掌握接口模块的时序仿真图。图中,完成初始化后,该模块根据CMD指令,解析出对应的SDRAM操作命令。

图10是指令解析相应模块仿真时序图,该模块根据发来的读、写、刷等命令,对SDRAM的掌握旗子暗记RAS_N、CAS_N、WE_N、CKE进行编码。

4结论

本文首先先容了基于FPGA视频采集系统的整体设计,对付采集和存储过程中实时性和高效性的哀求,分别谈论了ITU656视频解码中须要从采集到的视频数据中提取出有效视频数据流,以及将其调度为符合VGA显示的像素大小。在存储模块中,SDRAM的事情时钟和视频采集系统的时钟不同,为办理读写时钟不同步的问题,采取异步FIFO实现跨时钟域的同步化,同时采取了两片SDRAM实现乒乓缓存设计,对SDRAM掌握器各个模块分别进行Modelsim仿真验证,得出精确结果,可以知足系统的整体哀求。

参考文献

[1] 马峰,徐和根,赵曼,等.基于FPGA的智能卡掌握器的实现[J].微型机与运用,2013,32(1):2022.

[2] 沙晶晶.基于CPLD的VGA时序彩色旗子暗记的实现[J].微型机与运用,2013,32(1):5758,61.

[3]范兴山,彭军,黄乐天,等.基于OpenCL的FPGA设计优化方法研究[J].电子技能运用,2014,40(1):1619.

[4] 赵清华.基于FPGA的目标跟踪算法的设计与实现[D].西安:中国科学院西安光学精密机器研究所,2014.

[5] 祝长锋,肖铁军.基于FPGA的实时图像检测技能的研究[D].镇江:江苏大学,2008.

[6] 占文庆.基于FPGA的视频监控系统的设计[D].武汉:武汉理工大学,2014.

[7] 何云斌,张玉芬.多端口SDRAM掌握器的设计与实现[D].哈尔滨:哈尔滨理工大学,2009.

[8] 黄彪.基于FPGA的高清视频旗子暗记实时处理系统的研究[D].西安:国科学院西安光学精密机器研究所,2013.