设计目标:ZU11EG FFVC1760封装,挂载4组NVME,接口为PCIE X4 ,

先我们先对ZU11EG的资源进行剖析,在UG1075中我们可以清楚的看到其包含4个PCIE块,分别位于X0Y2,X0Y3,XIY1,XIY0.

在文档PG213上我们可以看到如下:

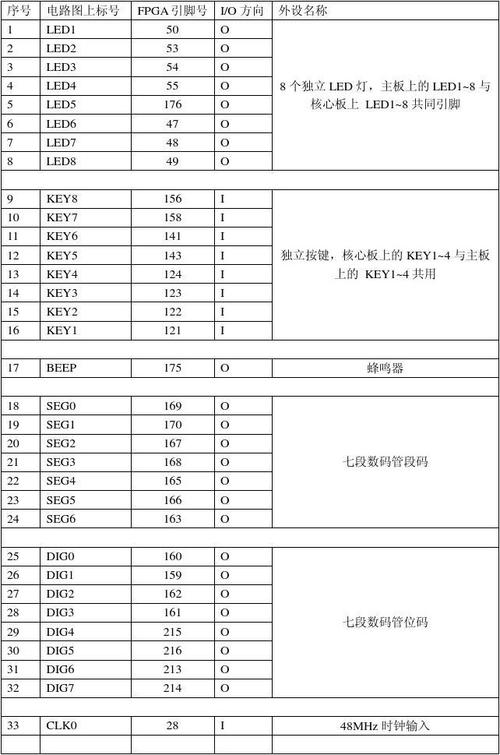

总结上文:在硬件设计引脚分配的时候我们须要知道:

1、一个GT Quad由四个GT车道组成。为PCIe IP选择GT Quads时,Xilinx建议您在最靠近PCIe硬块的地方利用GT Quad。虽然这不是必要时,它将改进设计的位置,路线和韶光。

2、须要把稳PCIE lane 0的位置

3.根据些表格,这些表格根据以下内容确定哪些GT库可供选择:IP自定义期间选择的PCIe块位置。

那如何验证自己的分配结果呢?终极在实际利用的时候我们会运用到干系的IP核,最大略也是最靠谱的方法,是采取vivado新建工程,天生PCIE的IP核进行验证,如下图所示,可以清楚的知道对应的那些可用。

在FPGA硬件设计中,引脚分配是最主要的一步,也是最关键的一步。