数据、算法和算力是人工智能技能的三大要素。个中,算力表示着人工智能(AI)技能详细实现的能力,实现载体紧张有CPU、GPU、FPGA和ASIC四类器件。CPU基于冯诺依曼架构,虽然灵巧,却延迟很大,在推理和演习过程中紧张完成其善于的掌握和调度类任务。GPU以捐躯灵巧性为代价来提高打算吞吐量,但其本钱高、功耗大,尤其对付推理环节,并行度的上风并不能完备发挥。专用ASIC芯片开拓周期长,资金投入大,由于其构造固化无法适应目前快速演进的AI算法。FPGA因其高性能、低功耗、低延迟、灵巧可重配的特性,被广泛地用作AI加速,开拓者无需改换芯片,即可实现优化最新的AI算法,为产品赢得宝贵的韶光。

由此,百度基于FPGA打造了EdgeBoard嵌入式AI办理方案,能够供应强大的算力,支持定制化模型,适配各种不同的场景,并大幅提高设备真个AI推理能力,具有高性能、高通用、易集成等特点。本文将紧张先容EdgeBoard中神经网络算子在FPGA中的实现。

FPGA加速的关键成分

FPGA实现AI加速有两大关键成分,一是FPGA内部资源,二是内存访问带宽。FPGA内部资源紧张包括LUT,FF,RAM以及DSP等,FPGA实质上是可编程逻辑电路,可用逻辑电路的多少取决于芯片内部资源,这也就决定了芯片的峰值算力和可容纳的算子种类数。

在深度学习中,90%以上的打算都集中在conv、dw-conv和pooling等少数的几个算子上。以是,并不是FPGA中添加的加速算子数量越多越好,而是要看重算子的加速质量:一是用更少的资源实现更多的功能;二是提高耗时占频年夜的算子性能。

在实践中,添加新算子前须要平衡该算子在网络中所耗韶光的占比以及其在FPGA中所花费的资源。当然可以通过选取更大规模的电影来打破这种限定,但是端上设备受限于本钱、功耗等成分,只能平衡多种成分选择一个得当规模的芯片,然后通过多种设计方法和技巧来提高加速性能。本文接下来就将先容在EdgeBoard中如何优化设计DSP资源提升算力,以及如何通过算子复用和领悟技能实现对多算子的支持。

提升内存访问带宽是提高AI加速性能的另一关键成分,由于FPGA与内存的数据交互在全体打算过程中占比很高,有时乃至超过了打算本身所花费的韶光。直接提高内存访问带宽的方法包括提高DDR位宽、增加传输所用的高速接口资源、提高DMA传输的时钟频率等。其余也可以通过复用FPGA芯片上的内存资源(RAM)以及打算和传输交叠实行(overlap)等方法,减少与外部DDR存储的交互,降落数据传输的开销。这些设计方法较为常见,本文不做详细先容。

两大关键技能实现四倍算力提升

FPGA中的打算紧张依赖DSP实现,高效利用DSP是担保FPGA算力的关键。EdgeBoard FPGA中的DSP采取DSP48E2架构,如图1所示,包括一个27-bit的预加法器(pre-adder),一个27x18的乘法器(mult)和一个48-bit的ALU。

图1. DSP48E2构造图

在EdgeBoard的FPGA设计中,充分利用DSP48E2本身的特点,采取supertile和INT8移位打算技能,实现了四倍算力提升。

一.Supertile

一样平常来讲,Xilinx Ultrascale系列FPGA运行的最高频率在300MHz到400MHz之间,但DSP是FPGA中的硬核,可以运行在更高的频率上。如图2所示,SLB-M与DSP这样构成的基本单元,被称之为Supertile,FPGA内部Supertile的布局如图3所示。Supertile技能的核心在于使DSP运行于两倍逻辑频率上,使全体系统算力达到倍增的效果。这紧张得益于芯片构造中SLICEM与DSP位置附近,利用专有的布线资源,延迟缩短,可以支撑SLICEM以双倍逻辑运行的频率向DSP供应数据。其余,神经网络中存在着数据复用,通过filter和image数据的复用和交织,一次取数多次利用,从而减少数据的搬运次数,提升打算效率。

图2. Supertile构造

图3. DSP和SLICEM在FPGA中的位置

二.INT8移位打算技能

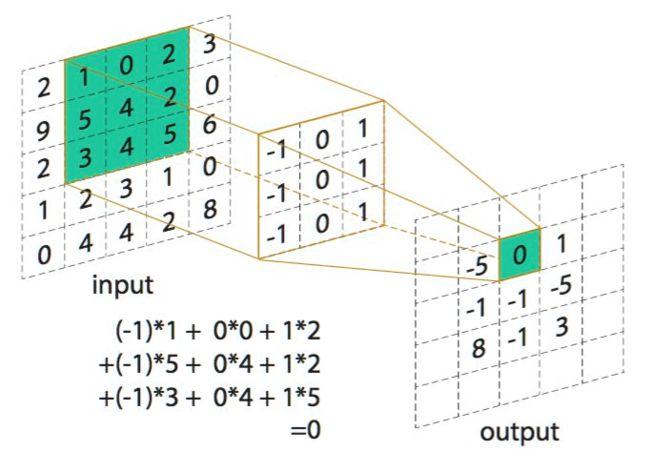

利用DSP48E2的构造特点,一个DSP完成两路INT8的乘加。在进行8bit数据打算时,将a左移18位,置于输入的高8位,低19位补0,从DSP的A端输入,b坚持在低8位,从DSP的D端输入,如图4所示。a与b两者前辈行累加,然后与c相乘后,结果将分别位于输出的高(ac)、低(bc)两部分,该打算过程如图5所示。

图4. DSP移位示意图

图5.单DSP实现两路INT8相乘

在实践中,我们把a,b两路作为filter数据输入,c作为image数据输入。这样DSP在一个时钟周期内就同时完成了两路的打算,再次使算力翻倍。结合前面提到的supertile倍频设计,两种设计使得单个DSP的算力提升四倍。由于一次打算过程有乘、加两个操作(operations),以是单个DSP在一个时钟周期高效的完成了8个operations。

多算子复用

深度学习中紧张有两类运算,一类是指数运算,另一类是乘加运算。前者紧张位于激活函数层,后者是深度学习涉及最多也是最根本的运算。乘加运算根据kernel的维度不同,又可分为向量型和矩阵型,在EdgeBoard中划分为三个运算单元,分别为向量运算单元(VPU: vector processing unit)、矩阵运算单元(MPU: matrix processing unit)和指数激活运算单元(EXP-ACT: exponential activation unit)。

一.向量运算单元

向量运算单元VPU卖力实现dw-conv(depth-wise convolution),完成3维输入图像(H x W x C)和3维卷积核(K1 x K2 x C)的乘加操作。个中一个卷积核卖力输入图像的一个通道,卷积核的数量与上一层的通道数相同,该过程如图6所示。图7表示的是一个通道内以kernel 2x2和stride 2为例的打算过程。

图6. dw-conv示意图

图7. dw-conv的打算

EdgeBoard通过复用VPU一套打算资源实现了average/max pooling,elementwise add/sub,scale,batch-normalize,elementwise-mul和dropout等多种算子。

1.Average pooling可以看作是卷积核参数固定的dw-conv,即将求和后取均匀(除以卷积核面积)的操作转换成先乘以一个系数(1/卷积核面积)再求和。如图8所示,该例子中卷积核大小为2x2,卷积核参数即为1/4。卷积核固定的参数可以类似于dw-conv下发卷积核的办法由SDK封装后下发,也可以通过SDK配置一个参数完成,然后在FPGA中计算转换,这样节省卷积核参数传输的韶光。其余,max-pooling算子与average pooling的打算过程类似,只须要将求均值操作换成求最大值的操作,别的挖窗、存取数等过程保持不变。

图8. Pooling复用dw-conv

2.Elementwise add/sub完成两幅图像对应元素的相加或相减,不同于dw-conv的是它有两幅输入图像。如果我们掌握两幅图像的输入顺序,将两幅图像按行交错拼成一幅图像,然后取卷积核为2x1,行stride为1,列stride为2,pad均设置成0,则按照dw-conv的打算办法就完成了elementwise的打算。通过在FPGA中设置当前像素对应的kernel值为1或-1,就可以分别实现对应elementwise add和elementwise sub两个算子。该过程如图9所示。

图9. ew-add/sub复用dw-conv

3.Scale算子紧张在图像预处理时利用,将输入图像每一个通道的全部像素点乘以该通道对应的scale值,然后加上bias。如果我们将dw-conv的卷积核大小设成1x1,行列stride都设置成1,pad设置成0,卷积核参数值设成scale,就可以通过dw-conv完成scale算子的功能。通过剖析创造,batch-normalize,elementwise-mul和dropout等算子都可以通过scale算子来实现。

二.矩阵运算单元

矩阵运算单元MPU卖力实现convolution,完成3维输入图像(H x W x C)和4维卷积核(N x K1 x K2 x C)的乘加操作,单个卷积核的通道数和输入图像的通道数相同,而卷积核的数量N决定了输出的通道数,如图10所示。full connection算子实现的1维输入数组(长度C)和2维权重(N x C)的乘加操作。将 full connection输入数组扩展成 H x W x C,输出扩展成 N x K1 x K2 x C,个中H, W, K1和K2均设置成1,这样 full connection就可以调用convolution来实现。其余,在打算 deconv时,通过SDK对卷积核进行分拆、重排,就可以通过调用conv来实现deconv,同样带来了极大的收益。

图10. Conv算子示意图

三.指数激活运算单元

指数激活运算单元EXP-ACT实现的根本是sigmoid,由于在FPGA中进行指数型运算比较耗资源,如何复用该打算单元就变得非常故意义。通过剖析创造,可以把 tanh和两通道softmax转换成 sigmoid的形式,这样一个指数运算单元就支持了3种算子,实现资源利用的最大化。

多算子领悟

在推理时做BatchNorm运算非常耗时,通过SDK将BatchNorm+Scale的线性变换参数领悟到卷积层,更换原来的weights和bias,这样4个算子可以领悟成单个算子conv + batchnorm + scale + relu,对付dw-conv同样如此。相对付每打算完一个算子就将数据送回内存,这种算子领悟大大减少了内存的读写操作,有效提高了处理帧率。

此外,我们将scale、bias和relu为代表的激活函数层放到各算子之后的链路上,然后统一送到DMA传输模块,如图11所示。这不仅使得各算子复用了这些逻辑,节省了大量片内资源,也使得各算子都可以具备这些功能,且都能以最大带宽进行DMA传输。在实践中,我们将这些功能做成可选项,由软件根据当前网络算子的须要进行选择,在节省资源的同时,既担保了通用性,又兼顾了灵巧性。

图11. EdgeBoard内部构造和链路图