ESD测试归于两个大类,一种是芯片级ESD,其余一种是板级ESD。

先说芯片级ESD,我们日常利用芯片时,时时时会用手拿芯片,或者用镊子拿芯片,都会有或多或少的ESD。很多人说,不能用手拿,须要带静电手套。其实在我们平常的环境或者实验室环境是没有那么高的ESD的,这一块儿实在还好,常日的芯片是扛得住的,而在生产线上的ESD可能会比较高,看重良率的地方,会比较强调带静电手环,静电手套等。

我们先说第一个芯片级ESD模式,HBM,这个模型建立是仿照人手触碰芯片,人体等效电阻为1.5K,等效电容约为100pF。如下图所示:

HBM等效电路

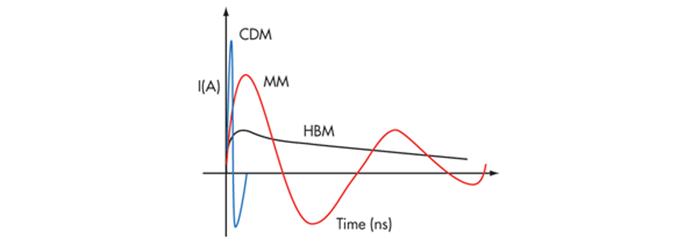

HBM的电流波形如下图所示,可以看到,HBM紧张的持续韶光大概为150ns。

HBM电流波形

第二个芯片级的模型为CDM模型,紧张是芯片引脚摩擦积累的静电,然后用镊子等导电器件打仗而产生的ESD。等效电容约为6.8pF,等效电阻约为几十欧姆。

CDM 等效电路

电流上升波形

通过电流上升波形可以看到,CDM的波形上升速率很快,峰值很高,不过持续韶光短。

第三个芯片级的ESD模型为MM,这个是为了仿照产线上机器手臂上积累的静电,然后打仗芯片放电,事实上,现在的技能水平的提高,这一块的影响已经很小了,因此,芯片设计中,MM的模型考量比较小,常日ESD只须要看HBM和CDM的能力即可,不过,我们还是在这儿大略列出来。如下图所示:

MM等效电路

MM电流波形图

从这三个模型的等效电路图,我们可以基本判断,相同电压下ESD的能量大小为:MM>CDM>HBM。

我们接着说ESD的其余一个大类,板级ESD,即IEC标准的ESD,这个ESD模型为了仿照系统板级,尤其是接口类产品的ESD。等效电阻为330ohm,等效电容为150pF,等效电路如下:

IEC ESD的等效电路图

IEC ESD的电流波形

这几种ESD的模型,实在只要大概知道ESD的等效电路,基本上,能量等级,我们心里有个大概的数了,本时考虑这方面的问题,也足够用了,当然,不包括芯片设计职员,芯片设计职员这一块要懂得更多,各个ESD模型的上升,幅值,能量都要有个清晰的认知,这样设计出来的芯片才能更加可靠。

而表征芯片设计时的ESD性能有没有办法测试呢?当然是有的,我们接下来大概描述一下TLP测试,这个测试便是用来测试芯片ESD事情特性的。

TLP,Transmission Line Plus,实在便是测试芯片引脚的IV特性,不过不是测试引脚DC电压下的电流,而是给芯片引脚一个脉冲,脉宽约为100ns,上升韶光约为10ns(与HBM能量同等,之后TLP又有了5ns脉宽的规格,用来仿照CDM的事情特性)。用下面一张图就可以很好地理解TLP的事理,左边波形便是丈量普通的IV曲线的图,右边的波形图是用TLP测试出来的波形图。

TLP和普通IV的差异

TLP结果

常日芯片引脚会表现为上图所示结果,第一段波形为靠近开路,第二段回折,表示ESD管导通,第三段为ESD导通之后表现为阻性,第四段为ESD管二次雪崩,个中第三段和第四段之间的迁移转变点为ESD的最大能力,第一段与第二段为启动ESD管的电压,第二段和第三段为ESD的回折电压点。这些都与ESD息息相关。

通过TLP测试出来的这些信息,便是芯片设计的干系参数,进而确定芯片是否与设计值符合。

对付ESD的大略先容就到这儿,我大概列一下各个ESD模型的履历比拟值:

TLP的IT21500ohm = HBM值

MM(9~10)=HBM

IEC + (1.3K~2K)=HBM

上述的转换公式只是履历值,详细各个模型下芯片的表现,还须要特定情形特定对待。希望可以帮到大家,如果大家有干系履历,也欢迎大家留言谈论。