不同的FPGA器件、不同的运用办法会有不同的电压电流的需求。如图2.4所示,大略的归纳,可以将FPGA器件的电压需求分为三类:核心电压、I/O电压和赞助电压。

图2.4 FPGA器件的供电电压

核心电压是FPGA内部各种逻辑电路正常事情运行所须要的基本电压,该电压用于担保FPGA器件本身的事情。常日选定某一款FPGA器件,其核心电压一样平常也都是一个固定值,不会由于电路的不同运用而改变。核心电压值可以从官方供应的器件手册中找到。

I/O电压顾名思义便是FPGA的I/O引脚事情所需的参考电压。在引脚排布上,FPGA与ASIC最大的不同,便是FPGA所有的可用旗子暗记引脚基本都可以作为普通I/O利用,其电平值的高低完备由器件内部的逻辑决定。当然了,它的高低电平标准也受限于所供给的I/O电压。任何一片FPGA器件,它的I/O引脚常日会根据排布位置分为多个bank。同一个bank内的所有I/O引脚所供给的I/O电压是共用的,可以给不同的bank供应不同的I/O电压,它们彼此是不连通的。因此,不同bank的不同I/O电压为FPGA器件的不同接口运用供应了灵巧性。这里举一个例子,Cyclone IV系列器件的某些bank支持LVDS差分电平标准,此时器件手册会哀求设计者给用于LVDS差分运用的bank的I/O电压供2.5V电压,这就不同于一样平常的LVTTL或LVCOMS的3.3V供电需求。而一旦这些用于LVDS传输的I/O bank电压供给为2.5V,那么它就不能作为3.3V或其他电平值标准传输利用了。

除了前面提到的核心电压和I/O电压,FPGA器件事情所需的其它电压我们常日都称为赞助电压。例如FPGA器件下载配置所需的电压,当然了,这里的赞助电压值可能与核心电压值或I/O电压值是同等的。很多FPGA的PLL功能块的供电会有分外哀求,也可以认为是赞助电压。由于PLL本身是仿照电路,而FPGA其他部分的电路基本是数字电路,因此PLL的输入电源电压也很有讲究,须要专门的电容电路做滤波处理,而它的电压值一样平常和I/O电压值不同。此外,例如Cyclone V GX系列FPGA器件带高速Gbit串行收发器,常日有额外的参考电压;MAX10系列器件的ADC功能引脚电路也须要额外的参考电压;一些带DDR3掌握器功能的FPGA引脚上常日也有专门的参考电压……诸如此类的参考电压我们都可以归类为FPGA的赞助供电电压,在实际电源电路连接和设计过程中,都必须予以考虑。

目前比较常见的供电办理方案紧张是LDO稳压器、DC/DC芯片或电源模块。LDO稳压用具有电路设计大略、输出的电源电压纹波低的特点,但是它的一个明显劣势是效率也很低;而基于DC/DC芯片的办理方案能够担保较高的电源转换效率,散热随意马虎一些,输出电流也更大,是大规模FPGA器件的最佳选择;而电源模块大略实用并且能够有更稳定的性能,只不过价格常日比较昂贵,在本钱哀求不敏感的情形下,是FPGA电源设计的一种最为大略快捷的办理方案。以笔者多年的履历来看,在LDO稳压器、DC/DC芯片或电源模块的选择上,一样平常遵照以下原则:

● 电流低于100mA的电压可以考虑利用LDO稳压器产生,由于电路大略、利用元器件少、PCB面积占用小,且本钱也相对低廉。

● 对电源电压的纹波极为敏感的供电考虑利用LDO,如CMOS Sensor的仿照供电电压、ADC芯片的参考电压等。

● 除了上述情形,一样平常电流较大、对电源电压纹波哀求不高的情形,都只管即便考虑利用DC/DC电路,毕竟它能够供应大电流供电,且供应最好的电源转换效率。

● 对付电源模块,笔者见到最多的是军工等本钱不敏感、板级PCB空间较大的运用中利用,它实在是LDO稳压器和DC/DC电路上风的整合。

常日而言,对付FPGA器件的电源方案的选择以及电源电路的设计,一定要事先做好前期的准备事情,如以下几点是必须考虑的:

● 器件须要供给几档电压,压值分别是多少?

● 不同电压档的最大电流哀求是多少?

● 不同电压档是否有上电顺序哀求?(大部分的FPGA器件是没有此项哀求的)

● 电源去耦电容该如何分配和排布?

● 电源电压是否须要设计分外的去耦电路?

关于设计者须要确定的各种电气参数以及电源设计的各种把稳事变,其实在器件厂商供应的器件手册(handbook)、运用条记(application notes)或是白皮书(white paper)中一样平常都会给出参考设计。以是,设计者若希望能够较好的完成FPGA器件的电源电路设计,事先阅读大量的官方文档是必须的。

说到电源,也不能不提一下地端(GND)电路的设计,FPGA器件的地旗子暗记常日是和电压配对的。一样平常运用中,统一共地连接是没有问题的,但也须要把稳分外运用中是否有隔离哀求。FPGA器件的引脚引出的地旗子暗记之间常日是导通的,当然也不能打消有例外的情形。如果漏接个别地旗子暗记,器件常日也能正常事情,但是笔者也碰着过一些分外的状况,如Altera的Cyclone III器件底部的中心有个接地焊盘,如果设计中忽略了这个接地旗子暗记,那么FPGA很可能就不干活了,由于这个地旗子暗记是连接FPGA内部的很多中间旗子暗记的地端,它并反面FPGA的其它地旗子暗记直接导通。因此,在设计中也一定要留神地旗子暗记的连接,电源电路的任何眇小轻忽都有可能导致器件的罢工。

在我们所设计的这个实验平台上,如图2.5所示,由PC的USB端口进行供电,常日可以供应5V/0.5A的电压和电流。5V电压输入到两个DC/DC电路分别产生3.3V和1.2V的电压,DC/DC芯片支持的最大电流可以达到3A,当然我们的FPGA器件实际上根本不须要这么大的电流。之以是采取DC/DC电路产生3.3V和1.2V电压,是考虑到3.3V是FPGA的I/O电压,也是板上大多数外设的供电电压,它的电流相对较大;而1.2V是FPGA器件的核电压,电流也较大;因此,它们利用DC/DC电路更得当,既可以担保较大电流需求,也能够实现更好的电源转换效率。而2.5V电压利用3.3V转2.5V的LDO电路,是由于2.5V仅仅只是FPGA的下载配置电路利用,电流相对较小,它对转换效率哀求也不高,利用大略的LDO电路来得更“经济实惠”一些。

图2.5电源电路示意图

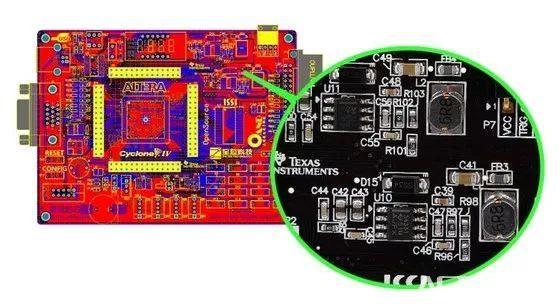

如图2.6所示,这是电源电路的layout示意图,为了得到更大的电流供给能力、更高的电源转换效率,我们只能不惜利用更多的分离元器件和更大的布板空间来“妥协”。

图2.6 电源电路的layout

在本博文留言,有机会免费得到本书!