什么是纳米制程?

首先纳米,是指一种长度单位,1纳米便是10亿分之一米,也叫毫微米。纳米制程,习气上,专指电子芯片中晶体管,极与极间距,电极本身宽度,从几十纳米到几纳米的长度间隔,比如十纳米制程,那么晶体管本身电极最小处便是10纳米。

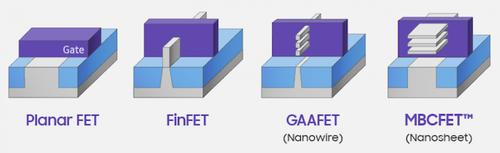

宏旺半导体理解到,一样平常而言,芯片的纳米制程便是指晶体管栅极的线宽度,也便是晶体管源极和漏极所连接的半导体材料的间隔。理论上,栅极的线宽越小越省电,电压也可以越低。

宏旺半导体剖析5纳米、7纳米等制程究竟是指什么?

根据摩尔定律理论,每隔18个月,芯片内部晶体管数量就会翻一番,性能也将随着翻倍。这样芯片性能不仅更加强大,而且功耗也会更低。随着芯片面积越来越小,集成电路内部晶体管数量急剧增加,在性能方面也会大大提升。举个例子,7纳米制程工艺的A13仿生芯片有85亿个晶体管,而5纳米制程的A14仿生芯片内部将拥有150亿个晶体管。

5纳米或将成为今年焦点

如果说2019年前辈工艺的竞争重点是7纳米+EUV光刻工艺,那么2020年焦点将转到5纳米节点上。根据台积电发布的信息,5纳米制程将分为N5、N5P两个版本。N5相较于当前N7的7纳米制程,性能要再提升15%、功耗降落30%。N5P则将在N5的根本上再将性能提升7%、功耗降落15%。

5纳米将利用第五代FinFET电晶体技能,EUV极紫外光刻技能也提升到10多个光刻层,整体电晶体密度提升84%。换句话说,以7纳米是每平方公厘9,627万个电晶体打算,则5纳米就将是每平方公里有1.771亿个电晶体。

纳米制程的进步对存储芯片有什么好处?

前文提到,缩减元器件之间的间隔之后,晶体管之间的电容也会更低,从而提升它们的开关频率。那么,由于晶体管在切换电子旗子暗记时的动态功率花费与电容成正比,因此,它们才可以在速率更快的同时,做到更加省电。其余,这些更小的晶体管只须要更低的导通电压,而动态功耗又与电压的平方成反比(这时能效也会随之提升)。

宏旺半导体之前说过,推动半导系统编制造商向更小的工艺尺寸进发的最大动力,便是本钱的降落。组件越小,同一片晶圆可切割出来的芯片就可以更多。

以是,纳米制程越前辈,芯片的性能越是刁悍,存储器产品越是优质。

宏旺半导体剖析5纳米、7纳米等制程究竟是指什么?

在制程技能方面,宏旺半导体一贯致力于eMMC/eMCP/DDR/LPDDR/UFS/UMCP

/SSD高阶存储产品的设计与制造。宏旺半导体自主研发前辈制程级别的eMMC,具有低功耗、高稳定度与轻小体积的特点,目前已广泛运用于移动设备、工规市场、车载系统、物联网、机器人及人工智能等领域。未来宏旺半导体会持续把存储芯片研发做好,连续对标国际原厂技能指标,达到国际一流产品技能标准,为市场供应最符合市场期待的存储办理方案。