FIB失落效剖析毛病不雅观察ictest1

一、FAB工艺流程入门•1. 这里的FAB指的是从事晶圆制造的工厂。半导体和泛半导体常日利用"FAB"这个词,它和其他电子制造的“工厂”同义。在平时沟通的语境中,FAB还可以被指代为“车间”,比如:在FAB事情的工程师上班时说:我进FAB了,实在指的是我进车间了。业界对付多个FAB,常日利用FAB1、FAB2…这样的编号来扩展。•2. FAB的车间是清洁室,进去要穿无尘服和专门的无尘鞋(配套的还有一次性网帽、口罩、手套),因此每个清洁室表面都会配套一个衣帽间,衣帽间和车间中间有风淋门隔挡,进去车间要测静电和过防护门吹掉身上的灰尘才可以进入。

上次去产线是真的。

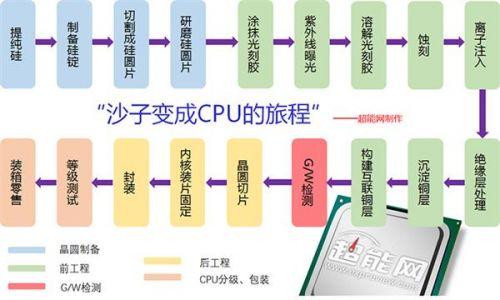

•3. 车间里面都是各种设备,每台设备会贴有设备ID,用以唯一识别它是它自己。总体上面可以分为两种:•一种是加工类:便是对晶圆进行增材、减材、改性的设备;•另一种是检讨类:包括检讨毛病、量测参数和测试电性。•检讨实在可再细分为检测、量测和目检三种,•检测紧张是针对毛病进行扫描,比如颗粒、图形毛病这些;•量测紧张是量出参数值,比如:膜厚、应力、电阻值、套准偏差这些;用显微镜和人眼看常日归到目检。•4. 加工设备和检讨设备配套组合在一起为工艺加工做事。工艺是车间内资源的有序组织形式,晶圆制造是一个循环加工的过程。 紧张是把立体的电路图形在衬底上给制造出来,由于是立体的以是就会有层(Layer)的观点,但是每一层的工艺是差不多。这些差不多的工艺,常日被概括为四大模组:薄膜、光刻、刻蚀、注入(扩散),每次工艺过后常日都会搭配量测或者检测工序,用以确定工艺的结果,比如,薄膜后就会要量一下膜厚,光刻和刻蚀后会要量一下线宽,扩散后会量一下片阻值之类,有些关键层还会要扫毛病。全部做完,要测电性。

二、四大模组模组是分工的产物,旨在让人能够聚焦于特定的一些工艺而不是全部工艺,达到熟能生巧,以确保工厂的稳定。

模组,实在便是把类似和干系的工序组成一个凑集的观点,这样就可以分配给相对的部门去卖力,他们只做这一部分对应的事情。比如:刻蚀工艺工程师就专门做刻蚀这一部分事情,不要做薄膜的事情。

模组是一个基于工厂管理的观点,而不是一个严谨的科学分类,因此四大模组显然是不能够概括所有工序,只能大体上用于理解制造的过程。要对晶圆制造过程有一个相对构造化的理解还得去剖析这个产品本身。

在电子天下里,二进制是万物的根本,通过1和0可以表征繁芜的掌握和运算逻辑,而二进制与物理天下的对应关系便是“开”和“关”,一台打算机就可以理解成是由一系列开关组成的电路的凑集。

一按开机键,就改变了电流,它被芯片翻译为0和1的的指令到存储器进行转换(通过门电路),然后输入到CPU的掌握单元进行转换,再输入到CPU的运算单元(一堆门电路组成的电路,实现读取指令,剖析指令,读取指令值(如开机) ,实行指令),算完之后,输出给外设(输出指令结果),比如显示器,显示器里面的每个晶粒通电,于是屏幕亮起。

其他的各种指示灯同理,依次亮起。这便是为什么打算机启动的出发点一定是要开机,通过外部给予一个触发的缘故原由。同样,很多软件的运行,也一样至少须要一个外界给予触发,触发之后就可以通过事先组合好的“0和1指令”(开关)去自运作。

这些开关显然不是一个一个装上去,而是一个模块一个模块组合好之后作为部件再组合在一起的。所谓,芯片便是把这些开关(实际上还有其他元器件,但是理解时可以忽略括号里面的这句话)集成在一起的模块,也便是集成电路。为了合营开关更好运作,还要有一些电压,电阻,电感,电容的界线值掌握,确保其功能ok和寿命足够。

集成电路里面的一个开关,常日便是一个晶体管,比如MOSFET。

开关与开关之间还要有金属互联才能浸染,这便是电路。

一堆开关通过金属互联组成一个繁芜的网,就形成了繁芜的逻辑电路和掌握电路,于是电脑就可以通过触发后就自动运作,各种电器就可以通过触发后就自动运作。

当然,如果要存储数据的话还要有电容,电容在微不雅观天下里,便是两片金属板,充电便是1,放电便是0,一系列的电容搭配上mosfet就形成了内存芯片。

FAB厂干的活便是在衬底上来制造出这样的电路:开关(晶体管)+其他器件(如电容)+连接导线(金属互联),做完之后,不能袒露,因此还须要有个保护层,便是钝化处理。

做好之后就交付给下贱封测厂去切割和封装与测试,变成可交付给电子厂的部件,比如CPU(包括掌握单元,运算单元等)、内存条等等。

衬底是制造电路的原材料,它是光滑的原片,FAB厂会在上面进行图形化,然后通过增材减材和改性处理,把一堆类似的电路立体式地制造在上面,变成可出货的成品。

开关有两种,一种是通电就打开,一种是断电才打开,我们要同时做两种开关,便是所谓的CMOS(CMOS能耗比纯挚的PMOSFET和NMOSFET这是工程演进的一个结果。

从电子管到晶体管锗晶体管,Si晶体管,PMOSFET和NMOSFET,CMOS,是对性能和运用侧场景问题不断办理和迭代的过程,现在前辈制程大部分是采CMOS工艺加工),其大致晶体牵制造、金属层堆叠、钝化层保护的工艺流程如下:

a 晶体牵制造(CMOS)

STI:隔离出一个一个井的边界,让开关只在这个边界里面加工。

NW/PW:注入离子,形成N井和P井

栅极制造:形成N井和P井的栅极

源极和漏极制造:注入离子形成源漏极,N井注入P,P井注入N,形成两个PN结。

N是negative,P是positive,N便是引入负电荷,也便是多余的电子,P是引入多余的正电荷,便是空穴。

电子和空穴称之为载流子。源极到漏极的方向是载流子的运动方向,也便是载流子是从源流入到漏(源头流入一个漏洞,再通过漏洞流到电源)

•PMOS便是正(P)电荷从源流到漏,•NMOS便是负(N)电荷从源流到漏

电流是正电荷的流动方向,因此NMOS和PMOS的电流方向相反。

而NMOS和PMOS里面的N和P指的是沟道里面载流子是电子还是空穴来定义的,沟道的浸染是联通源和漏,因此源和漏极里面添补的是啥和沟道内的电性又是一样的,以是,源极和漏极是引入N的便是NMOS,是P的便是PMOS。

bravo !

由于PMOS和NMOS电流方向是相反的,以是,把它两的漏极连起来,就会得到一个从PMOS的源极到漏极再从NMOS的漏极到源极的CMOS电路。

也便是一个非门电路:输入端A低压,输出端B便是高压;输入端A高压,输出端B便是低压。

•不同的连接和组合办法,形成基本的门电路,•不同门电路组合可以实现四则运算,构建起电子天下运算的根本,•再加上电容器的利用,则存储的问题也被办理。

能打算又能存储,那么运算器和存储器就可以被制造出来。它们不同的组合和连接,就可以得到不同的芯片,比如内存芯片,CPU芯片。

低阻值层:栅极、源极和漏极表面要天生一层低阻值物,用于后续金属互联层的链接点。

上面的加工过程并不是一个一个开关去加工的,而是全部一起加工,因此以sti边界为例,便是先涂满胶,再把边界要加工的边界显示出来,然后去掉边界的胶,再全体处理。

这样没胶的是我们要的,有胶的是我们不肯望被加工到井边,用胶覆盖住的井里,加工完再把胶去掉,这样边界就加工出来了,后续再在这个边界里面用类似的批量处理方法去一起加工出出一堆由源极、漏极和栅极组成的开关,一堆比如可以是几千万个或几亿个,乃至百亿个。

这些晶体管连在一起就形成一个die(一个井),也便是所谓的裸芯片,也叫管芯。

STI是Shallow Trench Isolation的缩写,意思是浅槽隔离。STI边界是指相邻STI构造之间的界线或分边界。较光滑和均匀的STI边界可以减少电场浓度和电流泄露,提高芯片的可靠性和性能。

一个die有多少个晶体管以及它们怎么连,常日是芯片设计公司会做好,变成版图,然后再交给FAB厂,这便是所谓的"集成"电路的观点。

b 金属层堆叠

底部器件制造完成之后,晶圆上就有非常多的MOSFET,它们彼此之间被绝缘氧化物隔离开,密密麻麻,但是又彼此独立。

为了让它们能够彼此协作进行事情,就要将这些MOSFET链接起来,这些链接物常日是钨,铜,也可以是其他金属。

连起来的这些晶体管,导通便是1,不导通便是0,由栅极进行掌握。电路越繁芜堆叠层数就会越多,比如几层到十几层。die便是一个芯片,根据尺寸不一样,一片晶圆上可以做几十到几万个die,末了要切下来封装。

6寸,8寸,12寸不同,还和沟道长度有关系,尺寸越大,做得越小,就可以产出越多,本钱就越低。si基现在8寸,12寸为主,6寸及以下要逐步淘汰,第三代半导体,比如SIC和GaN目前8寸能够量产的厂商还是个位数,6寸和4寸还有市场。

这里的寸指的是晶圆的尺寸,是用来表示晶圆大小的一种单位。不同尺寸的晶圆可以用光降盆不同的芯片,而不同尺寸的芯片则具有不同的性能和本钱。

c 钝化层保护

制造完成前面的器件层和金属层之后,还要加一层保护,比如SiO2或者SiN将其包裹起来,再开几个金属链接点用于后续封装利用(用于外部触发)。基本上Wafer制造过程就完成,可以交给封测厂进行切割和封装测试。

总体而言,晶圆来料表面是光滑平坦的,要在上面加工出错综繁芜的器件和金属互联线路,须要经由增材、减材和改性处理才行。

这些过程紧张和化学堕落与离子轰击有关。

•个中增材便是薄膜干系工艺,•减材便是刻蚀,•改性便是注入干系工艺,

还有便是上述三个处理过程发生的详细位置常日要在晶圆上画出来,以指示加工的范围,则是光刻的事情。

•ET:刻蚀,用化学或物理的方法做减材处理,分为干刻和湿刻,要刻得刚刚好,不能过刻也不能不敷,刻蚀率和选择比就很主要。选择比越大越好。刻蚀速率常日是固定值比较好,为了得到这个值就要常常做monitor,前量后量,再用公式算出来。刻蚀前常日会长一层氧化膜做阻挡层。刻蚀考虑的指标常日有:•Etch rate(刻蚀速率),•selectivility(选择比,相对刻蚀速率),•uniformity(均匀度,坑坑洼洼),•profile(刻蚀图形规则度:斜着刻,弧形还是垂直刻) ,•end point(终点的选择,到了就停滞再刻,比如要sio2)•TF:薄膜,在晶圆上面长膜,分pvd和cvd两种,膜厚,均匀度,平坦度很主要。要得到好的均匀度和平坦度,要在真空环境下来完成,为什么呢?由于真空环境,把金属气化之后就会变成无序四面八方去运动,就会更均匀。•DF:扩散/注入,扩散常日是把离子打到比较浅,再高温加热让它扩散到深处,注入是直接用能量打进去,不要加热,属于可以常温下下处理的一种工艺。要掌握能力,剂量和角度。•PH:黄光,车间里面这个区域的灯都是黄色的,包括涂胶,曝光,显影三大工序,胶分为正胶和负胶(负胶是曝光部分显影后会留下来,正胶则相反,可以把负当作“附”着来赞助影象),

事理是:光刻胶中含有感光剂,被照射后会发生化学反应,使得被照射部分和未被照射部分,打仗到显影液时候的溶解速率相差三个数量级(比如3000)倍旁边。

曝光时候,能量,焦距和曝光韶光很主要,会影响尺寸和图形的品质,在确定参数时,都会先做FEM(focus enerage matrix)。

光刻比较在意的有这样几个结果参数:

•分辨率,也便是一毫米宽的间隔可以画多少条清晰的线;•Overlay,也便是不同层之间的对准;•毛病,做完光刻,不能有残留。还有便是感光速率,太慢效率就低了,本钱会变高;•其余便是膨胀,温度会热胀冷缩,影响对准。

如前文所述,四大模组制造产品,过程当中也是要穿插检测进行丈量,防止不良造成后段工序涌现问题,比如:

•光刻不同层之间要确定套准偏差在规格以内,•刻蚀要关注刻蚀后的台阶,•薄膜要量膜厚等等。

做完之后,看产品,有些还有背金,便是把全体Wafer背面做减薄处理。

末了出货前,还要进行电性检测,以评价器件特性。

电性无外乎便是,电容、电阻、电流、电压,一讲就知道,只是把这些参数放到MOSFET的场景去而已。

如果把一个晶体管想象成一个开关,分为源,漏,栅极。栅极加电压,电流就会从源极流到漏极。这样一个大略场景,它的空想状态是:

•a.我要知道施加到栅极的电压是一个固定值,同一个开关不能变来变去,这个是Vt,另一个是Vt+n,否则随意马虎涌现,开关没打开的情形,这个Vt便是所谓的阈值电压(Threshold Voltage),也便是产生强反转所需的最小电压。这个值是客户根据利用场景设计时候就定好的,比如手机和汽车上用的MOS(开关),肯定就不一样。因此,FAB做出来的结果要靠近客户的设计值。•b.当Vt确定后,往栅极加电压,就要可以掌握电流,这个加上去的电压和被掌握的电流它们之间的关系以及自己的稳定性也要被规范。栅极电压叫Vg,v是电压,g是GATE,栅极的意思。

根据事理,当栅极电压Vg<Vt时, MOS处于关的状态,而Vg〉=Vt时,源/漏之间便产生导电沟道,MOS处于开的状态。否则就不是ok的mos。不同场景Vg,也常日希望是一个高于Vt的固定值。这样要打开开关,输入一个固定Vg就行,才不会涌现意外。

•c.那加了一个固定的Vg电流是不是稳定的呢,不是的,实际会受环境影响漂来漂去,比如温度高温度低之类。那就卡一下最大电流,便是所谓的饱和电流。

也便是在栅压(Vg)一定时,源/漏(Source/Drain)之间流动的最大电流Idsat,这里I是电流的意思。

•d.开时候有电流,关时候就要没电流,这才是一颗正经开关,可是实际上也是很难的,以是只能追求它越小越好。Ioff,这里I是电流的意思,ioff叫关态电流。

Vg=0时的源、漏级之间的电流,一样平常哀求此电流值越小越好。Ioff越小, 表示栅极的掌握能力愈好, 可以避免不必要的泄电流(省电)。

•此外,还有Vbk(breakdown)、Rs、Rc等等用以评价器件特性。而这些特性实在与前面工艺过程息息相关,比如Vt就与poly CD、Gate oxide Thk. (栅氧化层厚度)、AA(有源区)宽度及Vt imp条件有关。

丈量电性的是Wat和CP,个中,WAT是抽测(仿照器件,选几个点),CP是全检,会用到的探针卡,测到的ng的芯片,要用墨点掉,便是把晶圆上ng的那一些芯片打一个墨点,这个工步叫ink,封装厂到时候就不会去封装这些带墨点的die,以及外不雅观考验和Packing真空包装出货。

后道和前道的信息流要确保通畅,才能有效防止不良品不会流到终极消费者手中。因此工厂里面就要有CIM系统来做制造赞助管理。

NG是指不良的芯片,而INK是指对不良芯片进行标记或识别的过程。

•CIM系统:打算机集成制造系统,它不是一个别系,而是与制造过程强干系的一系列系统的总称,包括:•MES系统、•EAP系统、•RMS系统、•PC系统、•SPC系统、•YMS系统、•RTS系统、•RTD系统、•AMHS系统等。•MES:生产实行系统,用于管理车间的生产过程,起到防呆和追溯的浸染,是工程师利用最多的系统,工艺,设备和制造岗位险些每天都要用到它。•EAP系统:设备自动化掌握,上料后,系统会自动从上位系统,比如MES、RMS、APC获取run货信息给设备下指令加工,加工后把机台数据采集起来传给不同的系统进行统计剖析和掌握。•SPC系统:每次加工完成会有量测值,要进入到这个别系去进行剖析,剖析结果有非常就会自动限定机台和lot的流动与运行。•APC:参数调优,比如根据光刻套准偏差打算补偿值,实现自动调度机台参数。•YMS系统:不同的Layer,要系统来进行叠图剖析,形成终极MAP图,喂给机台进行加工,实现MAP Control。•RTS和RTD:实现算法自动派工,达到车间效率最佳和平准化生产。•AMHS:自动物料搬运,用天车实现Lot运送。

晶圆厂表示的是制造的最高水准,每天海量的数据,靠人工无法处理,基本上都须要IT系统来完成,通过人机系统的协同,实现稳定和高质量的交付。

晶圆厂表示的是制造的最高水准,工业化目前最高水准的表示。

工业软件追求的是一个稳定和防呆,常日技能比较旧,难用,界面密密麻麻一堆参数,功能模块有几百个。

曾经去产线,看到的ATE的机台上面有个一个极简的辅导文档被粘贴在机台上,每个案件也被标注了step。

一个FAB常日要配一个一定规模的IT团队对其进行掩护和不断地二开。

半导体厂追求的full auto,日常事情很多都要通过系统来完成,比如做实验,就要在系统开单,解Hold也要在系统做动作等等。

因此模组工程师除了学习工艺和设备干系技能外,还要学习不同的系统操作。这些系统有些是国产,有些是舶来品,有些是外购有些是自研。

但是好在它们都是环绕着晶圆制造的业务在做事,因此,功能做事工具是差不多,术语也大体同等,比如Secsion,你在这一家系统看到和其他家系统看到,它的意思都是一样的。

一片Wafer从投片到出货,会经由几百步骤乃至几千步。

前面的衬底制备,和后面的成品检测外,中间的步骤便是一层一层的薄膜、光刻、刻蚀、扩散的循环,每一个层便是所谓Layer,层与层之间要对准,否则就有可能影响器件特性。

而影响层与层对准的可能是工艺参数,比如涂胶时候的转速导致涂胶不屈均进而影响曝光之类。大概工艺影响的链条是这样:

•工艺参数(Recipe参数)、•工艺特性(cd/ovl、profile…)、•器件特性(Wat可检出电性:Vt、Ron、Loff、Rcvia、Rsheet、Continuty…;CP可检出电性:RT/HT、Vt、Ron、Ioff…)、•产品利用性(可靠性),

日常剖析的空想状态便是要去把握它们之间的Corelation剖析。

如果在详细产品的制造过程中,如果我们知道机台的某个参数,比如:压力、功率,它会影响到终极CP的哪个详细器件特性,比如击穿电压之类。

就可以将其集成到CIM系统里面进行卡控。日积月累形成制造系统知识库,让车间的抗扰动能力不断加强,以提高良率、效率和降落单件本钱。

基于这样的目的,要有一堆人用系统的术语理解,从事不同的岗位,共同努力才能实现。

三、术语总结3.1 与人干系

3.1.1 事情岗位

•CE:卖力对接客户的工程师•TD、RD:技能研发部门•PIE:制程整合工程师,类似产品经理和PM的角色,和客户对接理解客户需求带回厂内,折衷各个部门,评估量产可行性,关注终极产品的电性是否符合。•PE:工艺工程师,简称工艺 根据规格哀求设定机台的Recipe,提升生产效率和良率。•事情日常:刷邮件有没有被highlight,有没有领导或者别部门的待处理事变;•夜班交卸事变:Hold lot处理、机台、产品干系事变的处理;•开会:Issue的处理、action item的进度;•处理 Hold lot、非常、各种项目帮忙事情;•hold 比例低落项目、良率提项目等•EE:设备工程师,简称设备 保持机台的稳定:日常保养,确保不发生问题 发生问题了,去找出缘故原由并办理。Down机要写报告,新机台的安装和调试 hold lot reduction,cip continue improve plan,parts 管理 ,sop制作,fdc 监控逐渐衰退的trendchart,提前改换零件等等。

这些都是一些管理、掩护和改进系统的观点,可能涉及莅临盆、运营、掩护等多个领域。以下是对这些观点的基本阐明:

•Hold Lot Reduction:这是指减少库存的一种策略。通过精确地预测需求,并保持合理的库存水平,可以降落库存持有本钱并提高资金的流动性。

•CIP Continue Improve Plan:这可能是指持续改进操持(Continuous Improvement Plan)。这常日是一种不断优化流程、减少摧残浪费蹂躏、提高效率的策略。

•Parts Management:这是指零件或部件的管理。包括零件的采购、存储、分发等环节。有效的零件管理可以确保生产的顺利进行,同时还可以降落库存本钱。

•SOP (Standard Operating Procedure) Creation:这是指制订标准操作程序。SOP是辅导员工如何进行日常事情的文件,可以确保事情的标准化和同等性。

•FDC (Failure Trend Chart) Monitoring:这是指对失落败趋势图的监控。通过追踪和剖析故障模式的趋势,可以提前创造问题,并采纳相应的方法防止故障的发生。

•Replacement of parts in advance:提前改换零件是预防性掩护的一部分。这常日涉及到预测设备或系统的寿命,并在其达到寿命之条件前改换零件,以避免生产中断或设备故障。

•PP:生产操持•IE:工业工程师•厂务工程师•MFG:制造部•YE:毛病改进工程师 事情日常:Defect Map,Defect trendchart剖析,Setup KLA Recipe,hightline Module,追踪process产生的问题,进行early Alert:DN以减小impact scope。比较关注毛病,创造问题highlight Module,请他们改进。毛病改进工程师(YE)的事情日常包括以下内容:

Defect Map剖析:这是一种可视化工具,用于显示毛病的分布情形,可以帮助YE理解哪些区域或产品线存在更多的毛病。

Defect trendchart剖析:通过剖析毛病趋势图,YE可以理解毛病随韶光的变革情形,从而确定是否须要采纳方法来办理这些问题。

Setup KLA Recipe:这可能涉及设置或优化自动检测毛病的脚本或程序。KLA(Key Laboratory of Advanced Technology)可能是一个实验室或研究机构,其研究的技能可能涉及自动化检测。

hightline Module:这可能是一个别系或工具,用于高亮显示或标记毛病,以便更随意马虎地识别和解决问题。

追踪process产生的问题:这意味着YE须要找出是什么导致了这些问题,以及如何在生产过程中预防它们再次发生。

进行early Alert:DN以减小impact scope。这可能涉及到尽早创造并报告问题,以便有足够的韶光来制订和履行办理方案,从而最大限度地减少对产品或做事的影响。

•TO:生产技能员 线上作业员,按照SOP进行作业。

SOP指的是标准操作程序3.1.2 职位

台厂在高端电子代工霸占环球半壁江山,公司都很大,几万人到几十万人不等,全体职位等级比较规整,他们貌似基本上实现了全行业标准化,一个协理出来,大概就知道是什么层级的管理层。

相对而言,大陆企业的职位体系就各个公司都有很大差异,一个经理你就不好知道他是什么样的管理层。

半导体行业受台湾影响比较大,全体职位体系就与台厂附近。

台厂范例职位等级是:线长(班长)、组长、课长、部长、专理、副理、经理、处长、协理、副总、总经理、副总裁、总裁(台)。

大陆半导体厂基本上也是裁剪利用这一套,基本上会有这些职务:班长、课长(科长、课经理)、经理(部经理)、处长、总裁这样,个中省去了一些大陆不习气的专理和协理这种称呼。

3.2 与设备干系

•Equip:机台•Equip Group: 机台组,代表的是一种加工的能力(Capability),比如:AA层 Photo 涂胶,代表这个能力组的设备可以加工此层的涂胶,它具备这个能力。能力组的属性还有许多,比如Recipe等。设备和能力组是多对多的关系,代表一个机台用不同的参数就可以完身分歧的加工,也便是具有不同的能力,按S95标准是利用Capability比Group更准确。•Recipe: 配方/菜单,用以定义机台某一组加工参数和job process的凑集。比如:感应到电影、抽最上面一片,进腔体1,抽真空至xx,过2min,移动到腔体2,利用xx参数加工xx韶光,破真空…,把电影放回原Slot(槽位)。这样一个包含传动、流程和过程参数组成的凑集就叫Recipe。•subEquip: 子设备,如chamber和loadport•Chamber: 腔体•Loadport: 上料口•job: 机台内部的加工过程,包括步骤以及每个步骤的腔体和对应参数和韶光等的一个凑集•打标机: 用激光技能在Wafer上面刻上ID•洗擦机: 打标会产生颗粒,因此须要进行洗擦•显微镜: 洗的干不干净,可以用显微镜看•涂胶机: PR Coat,通过旋转在Wafer上匀胶,分正负光刻胶两种,正胶见光去世,负胶见光活•曝光机: 给光刻胶曝光,将Mask的图形转移到光刻胶上,光刻胶是高分子有机物,叫光致抗蚀剂。比如负胶被光照随处所会发生交链反应,原来线型构造变成网状构造,到显影液中就不会去掉而被保留。正向光刻胶,则被照的地方会发生降解,而更随意马虎被显影液溶解。•大面积透光为明场光罩板(Clear Mask),大面积不透光为暗场光罩板(Dark Mask),GDSII定义的图形区不透光则对应为Clear Mask,反之则为Dark Mask•显影机:给光刻胶显影,让图形显示出来•DUV、EUV光刻机,是让图形缩小的设备。•Season片: 机台启动后,投个Season片进行暖机。不同机台或者Chamber的暖机机制差别很大,有些是For Recipe的,比如从A Recipe切换到B Recipe就要暖机; 还有是For idle韶光的暖机,比如停机多久就要暖机。当然,出了暖机还有冷机,便是比如切换到某个Recipe 必须冷却一段韶光才能Run货。•Constraint:机台限定,包括有正向约束,反向约束,goloden,唯一正向约束,个中,黄金约束是同组设备哪些可Run,哪些禁Run。•parts:零部件•ring:环,零部件的一种•target:靶材

3.3 与物料干系

•Substrate: 衬底,是由半导体单晶材料制造而成的晶圆片,是FAB厂从供应商采购的原材料,它也可以进行外延工艺加工生产外延片。•背面刻号: 衬底来料背面常日会有供应商刻的追溯ID,是一串数字和字母组成的流水码,叫T7 Code•Spec: 参数,来料关注的一些技能参数,比如厚度,电阻率之类的关键参数信息。还有工艺加工过程的参数也是叫Spec。参数常日会设置规格,超规格一样平常的处理是Hold•PN: 料号,不同供应商,不同材料参数的衬底会有不同的料号,和Raw material一样的意思,站在供货方角度叫PN,站在收货方角度就叫原材料。•EPI: Epitaxy外延片,经由MOCVD工艺,可以在衬底上长一层几微米的单晶,可以与衬底为同一材料,也可以是不同材料(同质外延或者是异质外延),由于新生单晶层按衬底晶相延伸成长,从而被称之为外延层。•Wafer: 晶圆,口语叫电影,是一个统称,该当是包含外延,加工过的衬底和裸片•DIE: 晶圆上面的一个芯片,也叫管芯,比如一片6寸的晶圆上可以制造3000个Die•Lot: 多少个晶圆组成的一个批次叫Lot,比如8片一个Lot,25片一个Lot这样,常日根据产品,这个数量有一个常规值。常日会用一个ID进行标识。•NPW片: 非产品片的总称,包括:构造片、监控片(Monitor)、QC片、Season暖机片、Dummy片•QC片: 定期检测机台参数是否OK,比如刻蚀速率、颗粒是否OK,就会投QC电影进去加工来检测参数•offline: 与Lot加工处理不干系的定义为offline,比如设备PM、NPW的处理过程、赞助工具的处理过程的一些数据监控•Inline: 与LOT加工直接干系的或者是监控LOT的参数属于Inline。•SPC: 统计过程掌握,用以监控生产过程的稳定性,是一套IT系统。包括:掌握图查询、非常查询等。比如膜厚,会监控单点规格和均值。超管控(OOC/OOS)会触发邮件报警和Hold,还有一些判异规则:比如连续七点上升或低落之类也会有相应处置。

SPC Rule常日要结合实际利用,比如tf的工艺特性是随着韶光推移,某些参数会逐渐低落,那么就可以启用连续低落的Rule。但是有些是非正态分布和连续的值,比如毛病数,这些就卡一个spec就行。在运用spc的时候,终极目标是持续减少普通缘故原由,捉住分外缘故原由,但是也要兼顾工程师loading。

客户给一个规格,比如99~100,工厂能不能做到,就要去抓在线数据,算出中央值和分布情形标准差,然后和客户哀求的高下限放在一起形成掌握图。每天这样算太麻烦,于是就有指标来帮忙,比如cp和cpk。

•cp知识理解便是制程能力,能力越强,颠簸范围越小,也便是cp值越大,颠簸范围越小。纯公式理解也是这个结论,客户哀求的规格Range/实际的6西格玛。颠簸小,代表分母小了,由于分子不变以是cp就大。一样平常大于1.33是好的。

但是颠簸大小之外还要考虑中央点均值,以是还要看cpk值。

•OOC/OOS:针对规格或掌握图的两对掌握线,比如目标值是100,ooc是-99.5和100.5(管控线)、oos是-99和101(规格线),OOC和OOS紧张是Range的不同。理论上oos就要报废的,可是实际事情中,由于人性,大家设置规格时候都会层层给自己buffer,以是也会涌现超过之后,还往下放的情形,只是开一个DRB做监控。•Batch:多少个lot和NPW组成的凑集,产品+非产品一起进去加工,出来后,把NPW拿去测颗粒(Particle),用来判断产品上的颗粒水平,NPW是光片上面没图形测得更准。比如:炉管常日都是多个Lot一起组成Batch放在晶舟投进去加工。•Hold: 把电影锁住不让今后流片,实行此动作的系统是MES•Hold Ratio:hold lot占WIP的比例,用来考察Module处理Hold lot的指标,常日会有不同部门都有自己的target,不能高于多少•wip:work in process,在制品•Release: 解锁,电影可以连续今后流•skip:跳步•ship:出fab的末了一步•Future hold: 提前设置好电影要Hold在未来的哪个工序•MES: 生产实行系统,用于管理生产过程的IT系统, 包括:•对生产过程和物理举动步伐的建模、•过程监控和追溯等功能,对下连接EAP、横向对接WMS、SPC系统和物流系统、对上连接ERP系统,也会和OA系统对接•issue: 产线涌现的问题,Triger Issue的成分很多,大概包括以下几个来源:工程师创造、系统创造、客户创造。常日系统创造的影响程度最小、工程师次之,客户创造最受重视,大部分是这样,不一定全是。•OP meeting:跨部门的生产会议。参会成员包括:Module、制造部、质量、TD、PIE、YE、MPC、操持、市场、厂务等,一样平常是一级领导参会。每天议题固定,紧张包括:投片和产出进展、重点批次的进展和提前准备关照、昨晚的Down机情形以及一些AR的跟进。其他部门的一些主要议题等。发生重大Issue一样平常要准备报告来op申报请示。是工厂里面主要的拉通对齐和highlight会议。•Particle: 颗粒,便是金属颗粒,灰尘这些附着物,会影响器件性能,这是半导体杀手。•OTD:on Time delivery,定时交货率

3.4 工艺方法干系

•PWQ:为了更好地回避晶圆之间工艺参数的涨落对确定工艺窗口的影响,可以在同一片晶圆上改变曝光能量和聚焦度,再用毛病检测的方法来确定最佳曝光条件。这一事情被称为工艺窗口的再验证(process window qualification, PWQ)•split:分批•merge:合批•optimize•parameter 的 correlation确认•SRC:split runcard,分片单,做实验时候要从主FLOW上开分片单,跑不同条件•PRS:process Release standard,工艺放行标准,开拓新工艺时候,Release要有一个标准。•Str:split testing release,小批量验证•mstr:mass split testing Release,大批量验证•BSL:baseline,基线,基准,baseline机台指的是作为基准的设备,比如第一台研发成功的设备,后续的就属于扩机设备,而baseline spec便是确定了作为基准的规格,这个是一个形容词,可以用在很多场景,这里只举例两个而已。•CD:关键尺寸•inspection:检讨•ADI:after develop inspection,显影后检讨•AEI:刻蚀后检讨,e是刻蚀,ai和adi一样•monitor:监控,比如做QC监控机台长膜是否正常

3.5 事情场景干系

•测机 做Daily Monitor,用以监控机台的THK(厚度)、PA(颗粒)、U%(均匀度),并形成offline Chart。•毛病监控 用KLA毛病检测机台扫创造Defect,于是Highlight defect 给PE owner,工程师就要确认SPC 有没有OOC和OOS,或确认FDC的log有否非常,若创造机台有问题,就会PM,PM时可能要Calibration 某些部件,PM之后,要确认BaseLine后,才可以Release给MFG。•Prob Card:探针卡,Wafer生产完成之后,出货前要做CP测试,用于连接Wafer和测试机台(tester)的治具。•MAP:晶圆制造是By Layer制造,中间生产的关键层会去扫Defect,末了成品会测Wat和CP,终极结果会把几层的结果做叠图,形成Map,再Ink掉fail Die。•解Hold lot 产线涌现Issue,MES hold lot,工程师确认创造是Q time 超 ,初步剖断不会产生Defect,也不会影响良率,于是做Release 处理,避免影响Hold Ratio•PCRB:Program Change Review Board,项目变更审查委员会 FMEA、PSM、DOE、SPC、Hold Rate、Rework Rate、PCRB、YE、8D Report•weekly:一周一次•bi-weekly:两周一次•MO:Miss operation double confirm•cip:continue improve plan•bsk:best known method 最佳方法•AI/AR:action item/request 应实行项目•fyi:For your information•ndr:non-conforming disposition report 非常单,全称忘却了 有问题开单处理•OCAP:out of control action plan失落控行动操持,比如EDC OOS了,第一步是确认量测数据有没有错,第二步是重新量,第三步是针对机台和电影的处理等等,这样的一个流程方案。•DRB:Disposition Review Board,针对lot,比如超Spec了往下放就要开drb进行追踪。•Event abnormal review:重大的品质事宜要开EAR,比如某个工序持续涌现同样的defect map。•mrb:material review board,重大物料非常要开MRB,大批量用错原材料,用错光刻胶等等•DRB,EAR、MRB:大概便是非常的处理流程,DRB是确认要不要追踪电性,比如介质厚度便薄可能会影响电容,就要追踪一下子,这个lot owner层级可处理。涌现重大事宜,就要启动EAR和MRB处置流程,这个流程层级更高,要提交8D报告。•FMB:Factory Monitoring Board

3.6 术语运用进阶

一个Lot,常日没一层都要做镜检、扫Defect,测CD、Defect会出MAP图,比如刻蚀不净和残胶等,CD可监控OOC、OOS进而知道在线工艺稳定情形,WAT会仿照器件测值,CP全测,为ink做数据支撑,defect叠图剖析也可支撑ink,终极得到shipping Yield。

•Lot:在半导系统编制造中,一个Lot常日指的是一批经由相同处理步骤的晶圆。镜检:这是一种通过显微镜对半导体表面进行仔细不雅观察的方法。它用于检测各种毛病,如刻蚀不净和残胶等。•扫Defect:这可能是一种利用激光或其他能量源来检测和识别半导体表面或体内的毛病的技能。•测CD:这里的CD可能是指关键尺寸(Critical Dimension),它是一个衡量半导体构造尺寸的参数。通过丈量CD,可以监控在线工艺的稳定性,以及判断是否符合设计哀求。•Defect会出MAP图:MAP图可能是一种表示毛病分布的可视化工具,类似于舆图。它可以帮助剖析和理解工艺中可能涌现的问题。•WAT:半导体硅片在完成所有制程工艺后,针对硅片上的各种测试构造所进行的电性测试。通过对WAT数据的剖析,我们可以创造半导系统编制程工艺中的问题,帮助制程工艺进行调度。•CP全测:这可能指的是对每个芯片进行全面的晶圆测试,以确保其符合规格和性能标准。•为Ink做数据支撑:这里的Ink可能指的是在晶圆上标记或识别不良芯片的过程。数据支撑可能指的是为这个过程供应必要的数据或剖析,以帮助确定哪些芯片须要被标记或隔离。•defect叠图剖析也可支撑Ink:这意味着通过对毛病进行详细剖析,可以进一步支持芯片的标记或隔离过程。•终极得到Shipping Yield:这是指终极产品的良品率或出货率。经由所有这些步骤和剖析后,就能确定终极产品的质量和良品率。

来源:半导体工艺与设备

半导体工程师

半导体履历分享,半导体成果互换,半导体信息发布。半导体行业动态,半导体从业者职业方案,芯片工程师发展进程。