一、项目背景明德扬(MDY)为中科院某所研制一款X射线采集和处理设备,该设备采取了AD8488和AD9244两款芯片进行X射线的采集,采取FPGA进行处理,并通过网口上送至上位机处理。

本文先容了AD8488和AD9244的事理,下一篇文章将先容X射线采集中碰着的问题,希望能对大家有所帮助。明德扬专注于FPGA方面的项目研发以及干系元器件发卖,有干系需求的,可联系我们。

二、AD8488简介AD8488是一款128通道仿照前端,为高性能数字X射线系统而设计。它的仿照通道由一个积分器和增益可选的单端转低阻抗差分输出组成。该仿照通道将X射线或光电二极管检波器网络的电荷转换成电压旗子暗记。通道由CMOS晶体管组成,这些晶体管采取范例高输入阻抗的CMOS门。该设备的积分器采取一系列可选电容值,产生与电荷有关的电压,可适应广泛地输入电荷值。单端输入转差分输出电压放大器位于积分器之后,在这里偏移和低频噪声电压从输入电压中减去。一条128:1通道差分MUX位于缓冲器之后,驱动仿照输出缓冲。同时还供应开关驱动器和某些数字计时功能;这些功能全部集成在255引脚BGA基板上。全部128通道的电荷转换是同步进行的,之后便采取7位地址编码天生顺序电压输出读数。一共两次序列,对全部128通道进行采样。逻辑掌握输入CS_A和CS_B分别选择通道地址的下限和上限64模块。

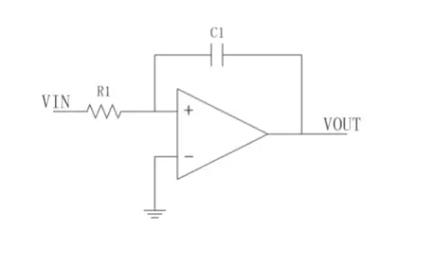

三、电荷积分放大器图1为运放积分放大器的电路图

图1:空想积分放大器电路图

根据运放虚短可知,反向端与同相端电压相等,又由虚断可知,通过R1的电流与通过C1的电流相等。通过R1的电流为:

通过C1的电流为:

以是:

由此可得,运放的输出电压即是输入电压在韶光上的积分。若输入端为电荷采集装置的话,那么运放的输出与输入真个电荷量成正比。两部分组合起来便是电荷积分放大器。

四、AD8488事情事理

AD8488电路构造如图2所示:

图2:AD8488电路构造图

如图所示,AD8488紧张由四部分构成。分别为前置电荷量转换器、差分输出选择器、输出缓冲器和时序/掌握部分。前置电荷量转换器为128通道电荷积分放大器,每一个通道由一个放大器,一个低通滤波器和一个二级放大器构成。电路构造图如图3所示:

图3:电荷量转换器构造图

前端采集到的电荷旗子暗记通过第一级积分放大器进行转换,共有四档可选。各档位转换参数如图4所示:

图4:电荷积分放大器转换参数

这四档分别由四种不同容值的反馈电容(CF1)掌握。当CF1=0.45pF时,输出范例值为2.3V/pC(单位为伏特每皮库伦,指每积分1皮库伦,输出为1V。1pC=10-12c);当CF1=1.1pF时,输出范例值为1.1V/pC,以此类推。CF1容值越大,增益越低。第二级低通滤波器实际上是一个保持装置,由一个电阻R1和一个电容CH构成。第一级放大器输出的电压旗子暗记通过R1给电容CH充电,以便于第二级放大器对CH进行积分放大。因此相称于一个低通滤波器。CH的参数由GNSEL[3..0]选择,参数如图5所示:

图5:CH参数选择表

注:GNSEL[3..0]寄存器只能选择CH的容值,并不代表增益。上图中所表示的增益实际上是当二级放大器的反馈电容为0.5pF是,不同的CH容值下对应的增益。第三级放大器与第一级相同,也是一个电荷积分放大器。只不过第一级输出的电压旗子暗记是对芯片输入的电荷量的积分,然后该电压旗子暗记对第二级的CH电容进行充电,之后通过第二级放大器对CH的电荷量积分,终极输出新的电压旗子暗记,形成二次放大的效果。第二级积分放大器增益由CF2掌握,共有10档,增益单位为V/V。注:由于第一级放大器已经将电荷旗子暗记转换为电压旗子暗记,因此第二级放大器的电压为伏特每伏特。增益表如图6所示:

图6:第二级积分放大器增益表

AD8488采集的旗子暗记经由两级放大后,经数据选择器选通通道后,再由一个缓冲器输出差分旗子暗记。该旗子暗记的幅度范围为1.5V至2.5V。官方推举利用AD9244这款ADC芯片进行仿照旗子暗记转换,推举电路如图7所示:

图7:AD8488与AD9244连接示意图

AD8488与AD9244共用一个2.048V的电压参考。AD9244的差分输出范围为0~2.048V,偏置电压为2.5V。

五、模数转换部分模数转换芯片选用ADI公司的AD9244,是一个14BIT,最高采样率为65MHz的高速ADC芯片。它由+5V仿照电压供电,也可以在+3.3V或+5V的数字电压下正常事情。

AD9244可专门用来处理峰峰值为1~2V的仿照小旗子暗记。它的输入旗子暗记和时钟旗子暗记都可以采取差分输入形式,以使系统得到最好的性能。14位数字输出旗子暗记可以表示为直接二进制的形式,也可以是二进制补码的形式。一位溢出表示位(OTR)可以用来输出溢出旗子暗记,将这一位旗子暗记和14位旗子暗记中的最高位用一定办法组合起来剖断输入旗子暗记是上溢出还是下溢出。VIN+,VIN-:仿照旗子暗记输入端。采取单输入形式时,在VIN+端接输入旗子暗记,VIN-端接地;采取差分形式输入仿照旗子暗记时,VIN+,VIN-分别接差分旗子暗记的两端。差分输入的形式对付高精度高速率的运用更随意马虎得到好的效果。一样平常情形下,输入旗子暗记都是单路形式,因此常常采取1:1变压器或者专用差分转换芯片来实现单路旗子暗记到差分旗子暗记的转换。

CLK+,CLK-:时钟旗子暗记输入端。和VIN+、VIN-相似,输入时钟也可以采取单输入和差分两种输入形式,不过在AD9244的内部终极都会把单输入的时钟旗子暗记变为差分形式。输入时钟旗子暗记的质量对模数转换的效果有很大的影响,因此应只管即便担保时钟旗子暗记的纯净和准确,并只管即便避免对时钟输入旗子暗记的滋扰。

DUTY:时钟稳定旗子暗记。该端接高电平时,可以在内部对外部输入时钟的占空比进行调度,以产生占空比准确为50%的时钟旗子暗记。

REFSENSE,VREF,REFGND:内部参考电压脚。这三个管脚的不同连接可以产生1V~2V的内部参考电压,在这三个管脚之间连接适当的电阻还可以随意产生1V与2V之间的任意电压参考。REFT、REFB:ADC内部参考电压去耦管脚。这两个管脚的输出电压是AD9244内部实际的参考电压值。它们之间该当用10μF的电解电容去耦,同时应并联一个0.1μF的小电容,这样效果可能会更好。每个管脚都必须用0.1μF的电容接地。CML,VR:AD9244内部利用的仿照偏压点,常日该端会产生大于300μA的电流,因此必须用0.1μF的电容接地以进行去耦。

OEB:输出许可管脚。AD9244有三态输出功能。如果OEB接地,那么AD9244的输出驱动器就会激活,并输出转换后的数字旗子暗记;而如果OEB接高,输出旗子暗记管脚则输出高阻态。DB0~DB13:数据输出脚,个中DB0为最低位。

OTR:电压溢出指示管脚。当OTR输出为1时,表示输入电压超过AD所能转换的电压范围。OTR和DB0进行大略的逻辑组合可以准确地判断输入电压是上溢出还是下溢出。DFS:输出数据形式选择管脚。当DFS接数字地时,输出数据为直接二进制形式;当DFS接数字电源时,输出数据为二进制补码形式。

本设计中的AD9244有以下几点设计要点:1)时钟采取差分的办法驱动。由于时钟旗子暗记和ADC的输出旗子暗记在一根排线内,ADC输出的并行数据会对时钟产生十分严重的影响,因此用差分的办法传输时钟。差分时钟在掌握板上分别由FPGA和AD9517产生,在调试时做二选一,用于验证两种时钟对采样时序以及信噪比的影响。时钟与ADC的连接办法如图8所示:由于掌握板产生的时钟旗子暗记为LVDS,因此在AD9244时钟输入端做互换耦合即可。

图8:AD9244差分时钟输入(互换耦合)

2)旗子暗记输入办法采取差分模式、直流耦合。AD8848的输出为差分旗子暗记,因此采取差分的形式与AD9244相连,AD9244旗子暗记输入端电路如图9所示:同时,ADC的VREF采取外部参考电压2.048V,因此单边旗子暗记输入的范围为1Vpp,差分旗子暗记的输入范围为2Vpp。又由于供电电压为5V,因此输入共模电压为2.5V。

图9:AD9244旗子暗记输入电路(直流耦合)

3)AD9244仿照供电电压为5.0V,数字供电电压为3.3V,这样就可以省却电平转换器,将ADC输出旗子暗记直接与FPGA相连。参考电压与AD8488共用一个芯片,为2.048V。由于利用了外部参考电压,以是须要将SENSE脚接高。AD9244为14位ADC,有效位数约为12BIT,因此在测试时,当差分输入正负两端相连,ADC上随机跳动的比特位该当是2bit,而输出的数值该当在8192附近跳动。当差分输入旗子暗记峰峰值为2Vpp是,ADC刚好打到满幅状态,超过这个电压,OTR为1,ADC溢出。

明德扬(MDY)除了承接项目外,还可为客户供应FPGA芯片、电源芯片、AD芯片等元器件,可找我们理解。